## **ULP POWER AMPLIFIER USING 65nm CMOS TECHNOLOGY**

## MUHAMMAD OVAIS AKHTER 02-281192-001

A thesis submitted in fulfilment of the requirements for the award of the degree of Doctor of Philosophy (Electrical Engineering)

Department of Electrical Engineering

BAHRIA UNIVERSITY ISLAMABAD

JULY 2024

# PhD-15

| Approval for | Examination |

|--------------|-------------|

|--------------|-------------|

| Scholar's Name: Muhammad Ovais Akhter Registration No02-281192-001                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Programme of Study:PhD Electrical Engineering                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Thesis Title:ULP Power Amplifier Using 65nm CMOS Technology                                                                                                                                                                                                                                                                                                                                                                                                 |

| It is to certify that the above scholar's thesis has been completed to my satisfaction and, to my belief, its standard is appropriate for submission for examination. I have also conducted plagiarism test of this thesis using HEC prescribed software and found similarity index $17\%$ that is within the permissible limit set by the HEC for the PhD degree thesis. I have also found the thesis in a format recognized by the BU for the PhD thesis. |

| Principal Supervisor's Signature:                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Date:12-07-2024 Name: Dr. Aurangzeb Rashid Masud                                                                                                                                                                                                                                                                                                                                                                                                            |

# PhD-16A

,,

## **Author's Declaration**

| I, | Muhammad Ovais Akhter      | hereby | state | that | my | PhD | thesis | titled |

|----|----------------------------|--------|-------|------|----|-----|--------|--------|

|    | LP Power Amplifier Using 6 |        |       |      |    |     |        |        |

is my own work and has not been submitted previously by me for taking any degree from this university

Bahria University

or anywhere else in the country/world.

At any time if my statement is found to be incorrect even after my graduation, the University has the right to withdraw/cancel my PhD degree.

Name of scholar: \_\_\_\_\_Muhammad Ovais Akhter

Date: 12-07-2024

## PhD-16B

## **Plagiarism Undertaking**

I, solemnly declare that research work presented in the thesis titled **ULP Power Amplifier Using 65nm CMOS Technology**

is solely my research work with no significant contribution from any other person. Small contribution / help wherever taken has been duly acknowledged and that complete thesis has been written by me.

I understand the zero tolerance policy of the HEC and Bahria University towards plagiarism. Therefore I as an Author of the above titled thesis declare that no portion of my thesis has been plagiarized and any material used as reference is properly referred / cited.

I undertake that if I am found guilty of any formal plagiarism in the above titled thesis even after award of PhD degree, the university reserves the right to withdraw / revoke my PhD degree and that HEC and the University has the right to publish my name on the HEC / University website on which names of scholars are placed who submitted plagiarized thesis.

Scholar / Author's Sign: \_\_\_\_\_ Mowais .

Name of the Scholar: <u>Muhammad Ovais Akhter</u>

#### ACKNOWLEDGEMENT

I would want to express my gratitude to Engr. Dr. Najam Muhammad Amin, in the strongest terms possible, who supported this work. I was able to complete all of the publishing phases of my project because to his direction and suggestions. He has been the ideal instructor, mentor, and advisor, providing guidance and inspiration with the proper balance of knowledge and excitement. I'm happy to have worked with him and am proud of him. I learned about wireless communication and analogue IC design for the first time in the course he delivered. Many of the concepts in this thesis were created with his assistance, and it builds on the work from previous classes.

Additionally, I want to express my gratitude to Engr. Dr. Aurangzeb Rashid and Engr. Dr Mukesh Kumar Maheshwari, for their brilliant comments and suggestions, and helping me developing my ideas. Without their guidance and persistent help this dissertation would not have been possible. To me, both of them are motivating teachers who paved the way for me while I was writing my thesis. I admire all the friends and co-workers that supported me in starting the project, sticking with it, and successfully delivering it. Particularly, Engr. Dr. Razia Zia made a lot of beneficial remarks and recommendations. She helped me to get the most out of my archive study.

Finally, I would want to thank all of my family members for their support and affection, especially my parents Jawed and Rana, my sister Beena, my wife Sunia, and my brothers Asad & Ghayas, for their ongoing assistance and support while I do my research and write my paper. They all kept me going, and this work would not have been possible without them.

#### ABSTRACT

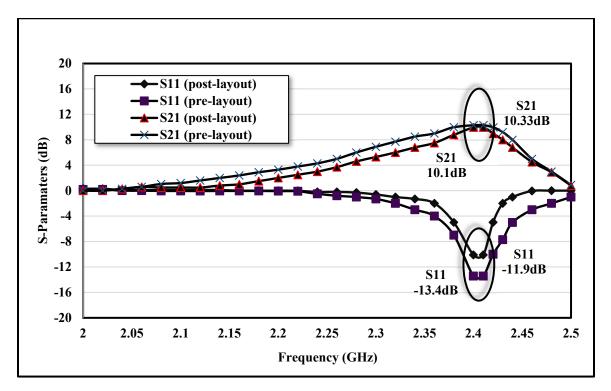

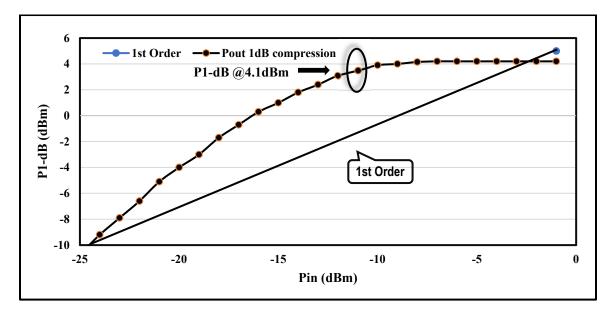

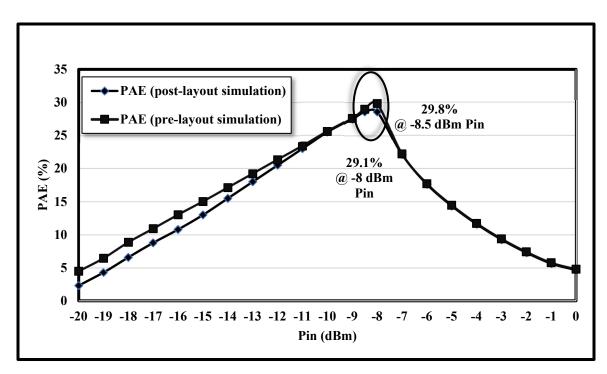

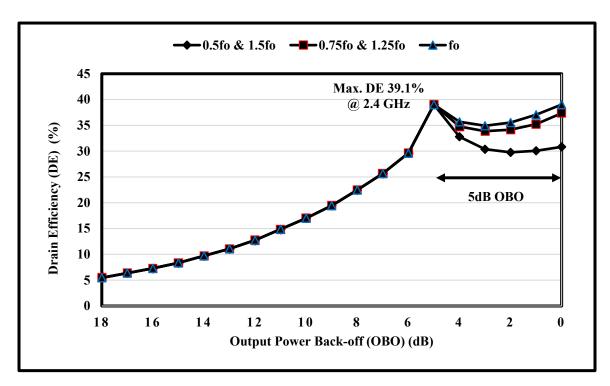

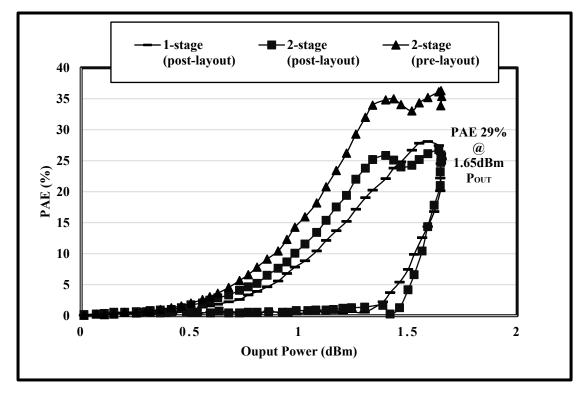

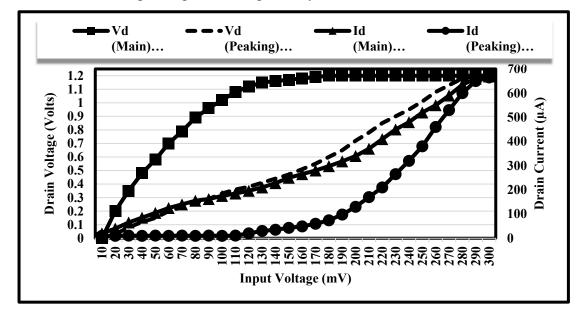

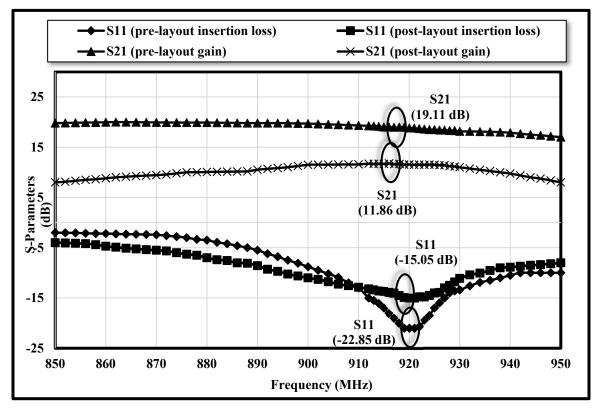

Power amplifier (PA) is the most power-hungry component of RF transceiver, portraying design issues. These include insufficient connectivity, power distribution, bandwidth, linearity and efficiency parameters that did not match system requirements. The primary challenge in a PA design is achieving higher efficiency while maintaining linearity over a bandwidth with wide range of output power levels. The power-added efficiency (PAE) is a figure-of-merit (FoM) that indicates how well the PA transforms DC power to RF power. Designers have raised concerns about PA in the front-end of wireless radios because of the system's significant power consumption. There has been a lot of study on PA methods for optimizing PA efficiency. It is a challenging measure in the design of PAs for various low-power IEEE 802 wireless standards. The result to this study's primary concern and problem is this issue, that presents the design and optimization of two ultra-low power (ULP) PA architectures using 65-nm CMOS technology. The first part of the dissertation is ULP Doherty PA (DPA) architecture with fixed interstage capacitances. The main amplifier and the peaking amplifier have been designed and optimized with power divider & combiner models using equivalent lumped parameters. Due to 40 MHz narrowband communication (2.4 – 2.44 GHz ISM band), it offers fixed capacitances before the input-impedance stages, for a perfect impedance matching at both stages. The novel design shows 2.1mW ultra-low DC power consumption, 29.2% PAE, and 4 dBm P1-dB compression point. The post-layout simulations show an extremely high gain of 10.14 dB, very low input-insertion loss of -11.9 dB, very strong drive current capability of 547µA & 663µA for main & peaking PAs respectively. Impedance matching is acquired to achieve the desired harmonic suppression at the output of DPA design. the consequences are all in comparison to state-of-the-art PA architectures for ZigBee and similar devices under short-range and low-power IEEE 802.15.4 WPAN standards. The second part of dissertation is class-F architecture with ET supply biasing to increase efficiency of overall PA design. The ET consists of a preamplifier before the envelope detector (ED) in a cascaded linear model, to increase

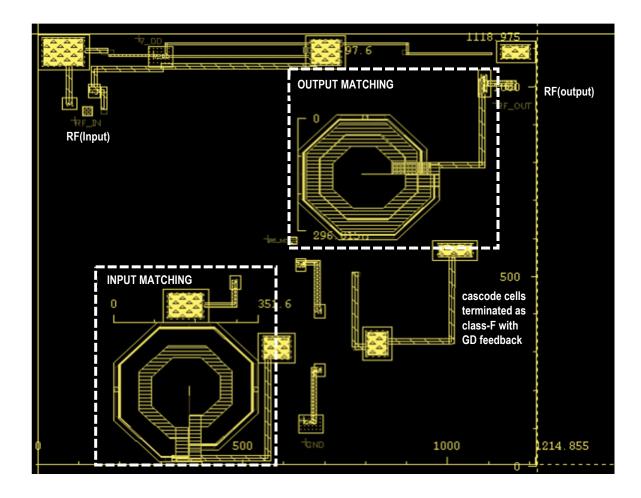

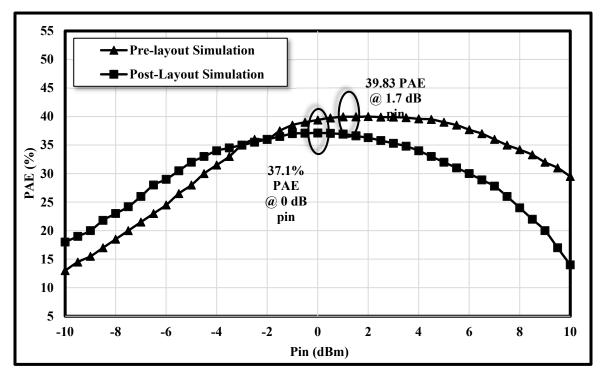

efficiency and to reduce DC power consumption. The gate-to-drain feedback in the PA's two cascode cells, terminated as class-F, helps to improve linearity and reduce harmonic content in the input signal. The novel design meets the requirements of the IEEE 802.11ah standard for long-range low power WLAN by using a DC power consumption of 3.75mW, a PAE of 37.1%, and an operating frequency in the unlicensed 915-931 MHz band in the United States. The chip layout size is reduced to just 0.13mm<sup>2</sup> by the ET inductor-less supply bias design.

**Keywords** - power amplifier, gain, ultra-low power, internet of things, power added efficiency, class-F, envelope tracking, gain, insertion loss, 65-nm CMOS technology

## **TABLE OF CONTENTS**

| CHAPTER |      | TITLE                                                          | PAGE |

|---------|------|----------------------------------------------------------------|------|

|         | TITL | E                                                              | i    |

|         | ACK  | NOWLEDGEMENT                                                   | ii   |

|         | ABST | ГКАСТ                                                          | iii  |

|         | TABI | LE OF CONTENTS                                                 | v    |

|         | LIST | OF TABLES                                                      | xi   |

|         | LIST | OF FIGURES                                                     | xii  |

|         | LIST | OF ABBREVIATIONS                                               | xvi  |

|         | LIST | OF SYMBOLS                                                     | xix  |

| 1       | INTR | ODUCTION                                                       | 1    |

|         | 1.1  | Overview                                                       | 1    |

|         | 1.2  | Background                                                     | 1    |

|         | 1.3  | Research Motivation                                            | 4    |

|         | 1.4  | The Theoretical Research Gap in Designing ULP CMOS RF I        | PA 6 |

|         | 1.5  | The Contextual Research Gap with Methodological Analysis       | in   |

|         |      | Designing ULP CMOS RF PA                                       | 7    |

|         | 1.6  | Problem Statement                                              | 10   |

|         | 1.7  | Research Contributions and Novelty                             | 11   |

|         |      | 1.7.1 Design and Optimization of 2.1mW ULP Doherty Power       |      |

|         |      | Amplifier with Interstage Capacitances Using 65-nm CMOS        | 5    |

|         |      | Technology                                                     | 12   |

|         |      | 1.7.2 Design and Optimization of High-efficient Class-F ULP-PA |      |

|         |      | using Envelope Tracking Supply Bias Control for Long-Ran       | ıge  |

|         |      | Low Power WLAN IEEE 802.11ah Standard using 65-nm              |      |

|         |      | CMOS Technology                                                | 13   |

|   |      | 1.7.3 Comparative Analysis of Design Parameters for Modern Radi | 0  |

|---|------|-----------------------------------------------------------------|----|

|   |      | Frequency Complementary Metal Oxide Semiconductor Ultra         |    |

|   |      | Low Power Amplifier Architecture Trends                         | 14 |

|   | 1.8  | Organization of the Dissertation                                | 15 |

| 2 | LITI | ERATURE REVIEW                                                  | 17 |

|   | 2.1  | Overview                                                        | 17 |

|   | 2.2  | IEEE Low Power Standards for Internet of Things                 | 17 |

|   |      | 2.2.1 IEEE Short-range and Low-power WPAN Standard              | 20 |

|   |      | 2.2.2 IEEE 802.15.4/ZigBee Power Amplifier Generalized          |    |

|   |      | Specifications                                                  | 21 |

|   |      | 2.2.3 IEEE Long Range and Low Power WLAN Standard               | 22 |

|   |      | 2.2.4 IEEE 802.11ah/WiFi HaLow Power Amplifier Generalized      |    |

|   |      | Specifications                                                  | 23 |

|   | 2.3  | The RF PA Classification and Design Techniques                  | 24 |

|   | 2.4  | Scope of Work for an Ultra-low Power High-Efficient CMOS R      | F  |

|   |      | Power Amplifier Design                                          | 27 |

|   |      | 2.4.1 Enhancing PA Linearization                                | 29 |

|   |      | 2.4.2 Enhancing PA Drain Efficiency and Power-Added Efficiency  | 29 |

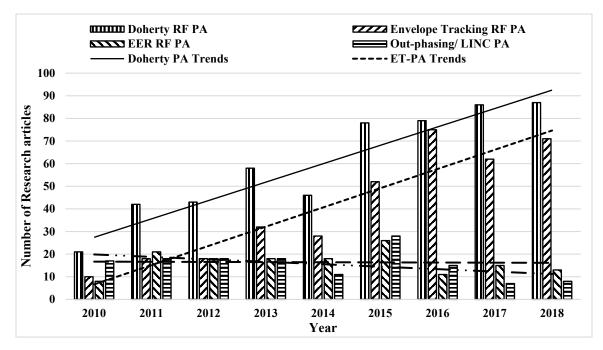

|   | 2.5  | Modern Trends in RF PA Design Architectures                     | 31 |

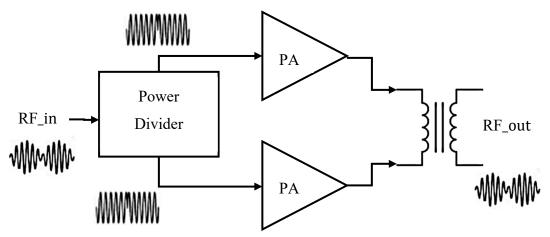

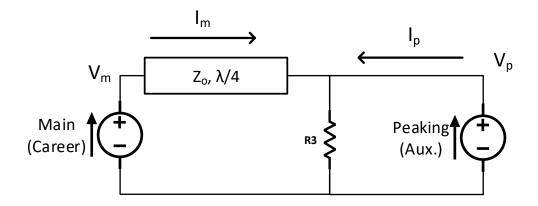

|   | 2.6  | Doherty Power Amplifier Design                                  | 33 |

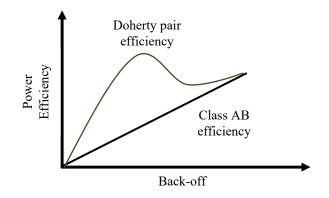

|   |      | 2.6.1 The Classic DPA                                           | 34 |

|   |      | 2.6.2 Modern Techniques in DPA                                  | 35 |

|   | 2.7  | Out-phasing / LINC PA                                           | 41 |

|   | 2.8  | Envelope Elimination and Restoration (EER)                      | 42 |

|   | 2.9  | Envelope Tracking PA Design                                     | 43 |

|   |      | 2.9.1 The Conventional ET-PA Architecture                       | 45 |

|   |      | 2.9.2 ET PA Design Trends                                       | 49 |

|   | 2.10 | Detection of Harmonics in OFDM Based Systems                    | 52 |

|   | 2.11 | Summary of Popular ULP Modern RF PA Design Architectures        | 53 |

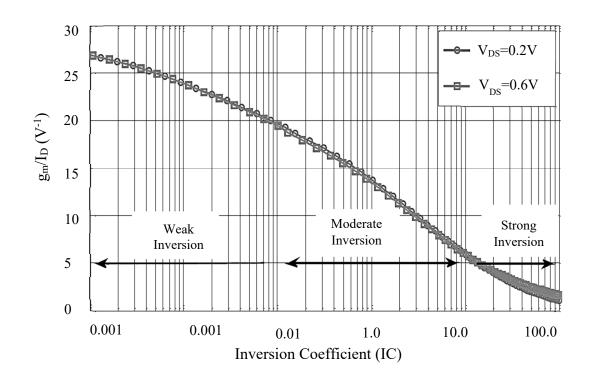

|   | 2.12 | Sub-threshold ULP CMOS Design                                       | 56   |

|---|------|---------------------------------------------------------------------|------|

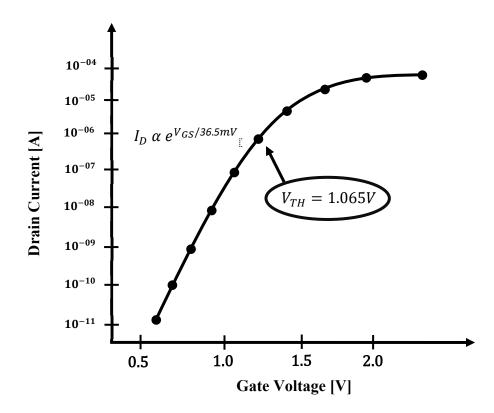

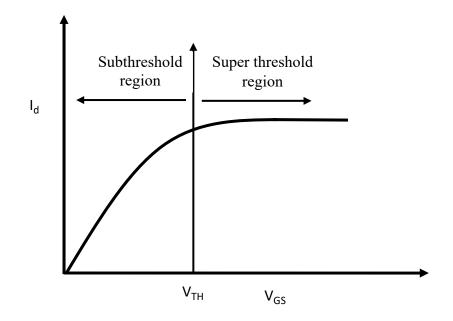

|   |      | 2.12.1 Subthreshold current                                         | 57   |

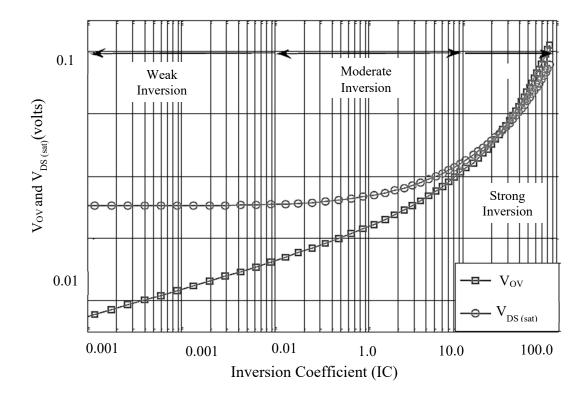

|   |      | 2.12.2 MOS Inversion Regions                                        | 59   |

|   |      | 2.12.3 DC Power Consumption Sources                                 | 61   |

|   |      | 2.12.4 Investigation of Subthreshold Gates' Characteristics         | 62   |

|   | 2.13 | ULP Design Biasing Scheme                                           | 63   |

|   |      | 2.13.1 Efficiency of Biasing Scheme $g_m/I_D$ – The Transconductant | nce  |

|   |      | Efficiency                                                          | 64   |

|   | 2.14 | Conclusion                                                          | 65   |

| 3 | RES  | EARCH METHODOLOGY                                                   | 68   |

|   | 3.1  | Overview and Research Epistemology                                  | 68   |

|   | 3.2  | Design and Optimization of ULP Doherty Power Amplifier (            | DPA) |

|   |      | with Fixed Inter-stage Capacitances for Short-Range and Lov         | V    |

|   |      | Power IEEE 802.15.4 WPAN standard                                   | 69   |

|   | 3.3  | The Development of DPA Model Using Ideal Components                 | 69   |

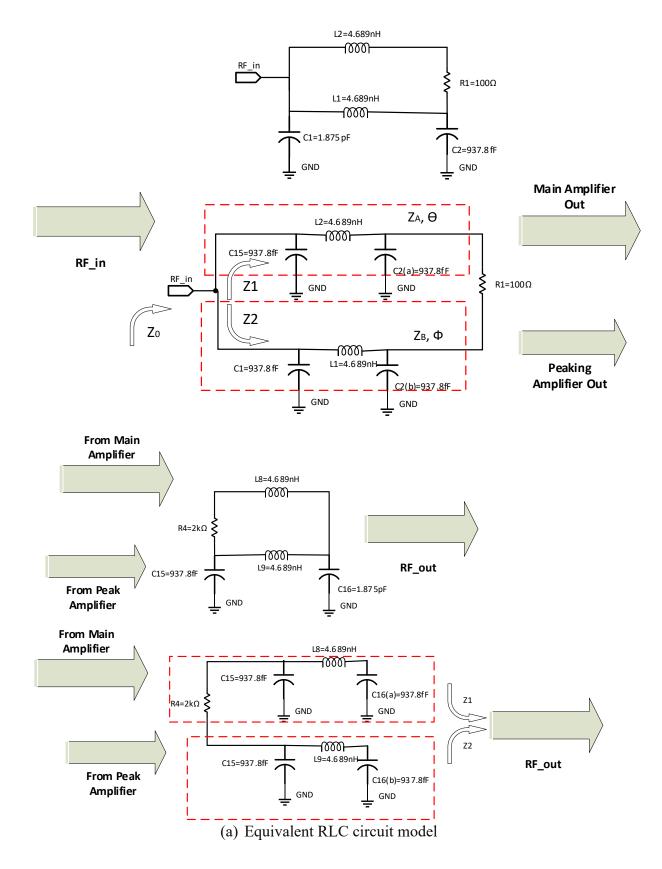

|   |      | 3.3.1 The Ideal Power Divider and Combiner Models                   | 71   |

|   |      | 3.3.2 Traditional Class-AB PA Model Validation and Load line        |      |

|   |      | Analysis using CAD Tool Analogue Library                            | 76   |

|   |      | 3.3.3 Analysis of Simulation Results for the Classic DPA using I    | deal |

|   |      | Components                                                          | 79   |

|   | 3.4  | The DPA Design, Simulation and Optimization in 65-nm CM             | IOS  |

|   |      | Technology                                                          | 82   |

|   |      | 3.4.1 Matching input and output impedances and small-signal         |      |

|   |      | modelling                                                           | 83   |

|   |      | 3.4.2 Subthreshold Operation in Weak Inversion Region               | 87   |

|   |      | 3.4.3 PAE, Power Consumption, and Small Signal Model for S1         | 1 &  |

|   |      | S21 Validation                                                      | 88   |

|   |      | 3.4.4 Effects of Parasitic Component on High Frequencies and L      | oad  |

|   |      | Pull Simulation                                                     | 91   |

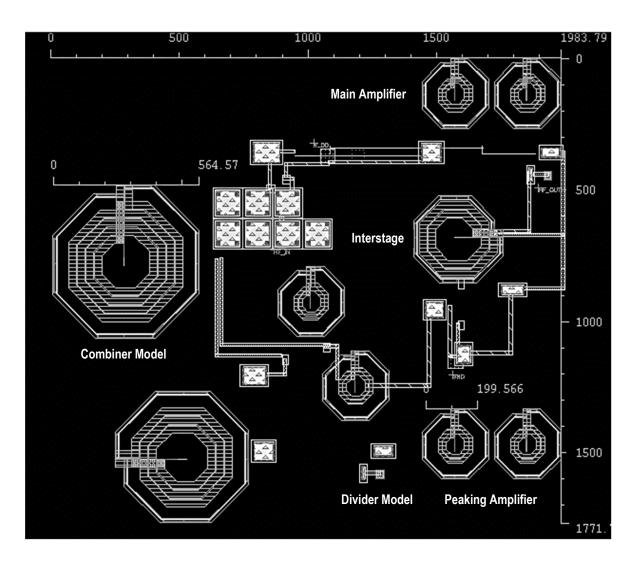

|     | 3.4.5 Layout of Proposed ULP CMOS RF DPA                    | 95         |

|-----|-------------------------------------------------------------|------------|

| 3.5 | Design and Optimization of Envelope Tracking (ET) Supp      | oly Bias   |

|     | with Cascoded Cells Terminated as Class-F ULP-PA for I      | long-      |

|     | Range and Low Power IEEE 802.11ah WLAN standard             | 98         |

| 3.6 | Requirement of ET Measurement System                        | 99         |

|     | 3.6.1 Comparative Analysis of OFDM BW Ranges for Genera     | ation of a |

|     | Modulated Signal                                            | 100        |

|     | 3.6.2 Measurement of Efficiency of PA                       | 101        |

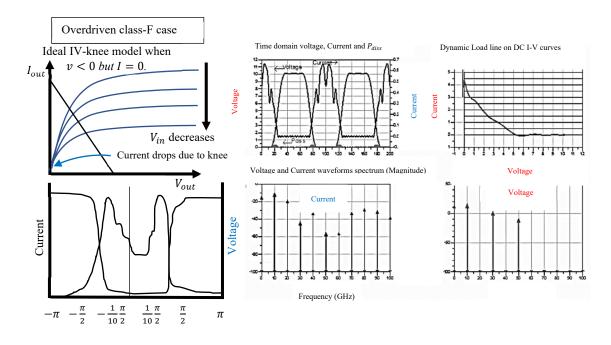

| 3.7 | Fourier Series Analysis of Input Harmonics and Its Impact   | on PA      |

|     | Design                                                      | 102        |

| 3.8 | The Proposed Class-F ULP-PA using ET Supply Bias in 6       | 5-nm       |

|     | CMOS Technology                                             | 108        |

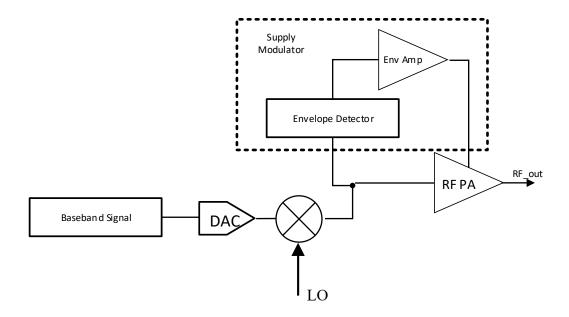

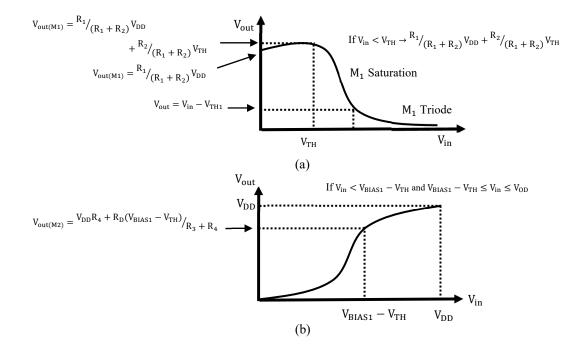

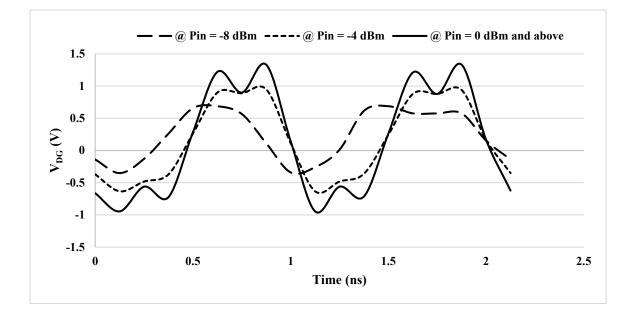

|     | 3.8.1 Pre-Amplifier Stage with Envelope Detection           | 109        |

|     | 3.8.2 ED Conversion Gain Using Source Follower Differentia  | l Circuit  |

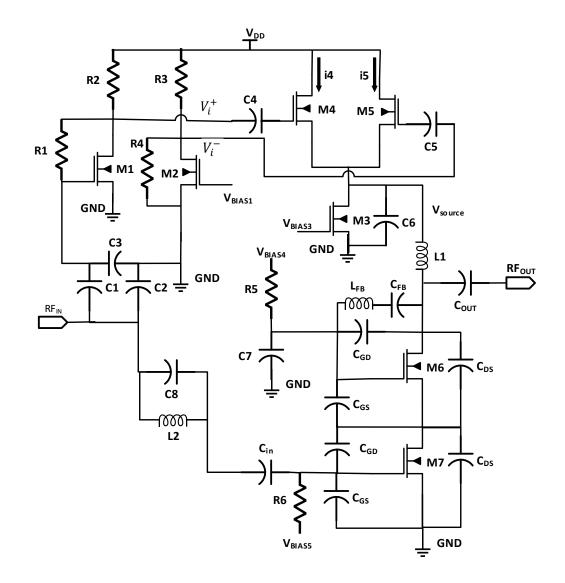

|     | 113                                                         |            |

|     | 3.8.3 Two Cascoded-Cells Terminated as Class-F with Gate to | ) Drain    |

|     | Feedback                                                    | 115        |

|     | 3.8.4 Power Consumption Under Subthreshold Weak Inversio    | n with     |

|     | Proposed Design Parameters                                  | 117        |

|     | 3.8.5 Layout of Proposed CMOS RF ET Supply Bias using Ca    | ascoded    |

|     | Feedback class-F PA                                         | 118        |

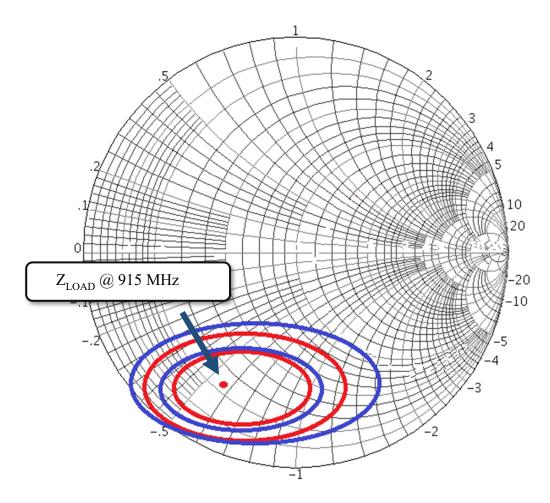

|     | 3.8.6 Analysis of load pull for class-F PA                  | 119        |

| 3.9 | Conclusion                                                  | 121        |

|     |                                                             |            |

|     | SULTS AND ANALYSIS OF PROPOSED ULP PA DESIGN                |            |

|     | CHITECTURES                                                 | 123        |

| 4.1 | Overview                                                    | 123        |

4

| 4.3  | Comparison of Performance Parameters of the Proposed ULP    | DPA  |

|------|-------------------------------------------------------------|------|

|      | with Current State-of-the-Art PAs for IEEE 802.15.4 WPAN    |      |

|      | Standard                                                    | 129  |

| 4.4  | Cost Projection Analysis for Proposed ULP DPA               | 130  |

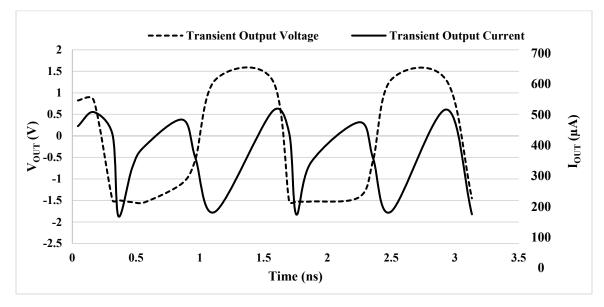

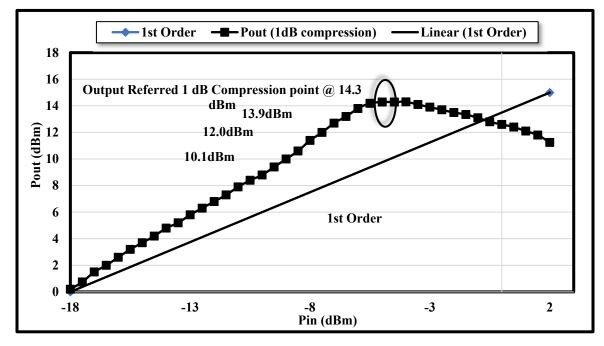

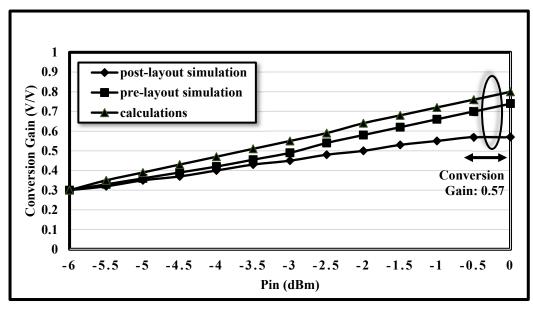

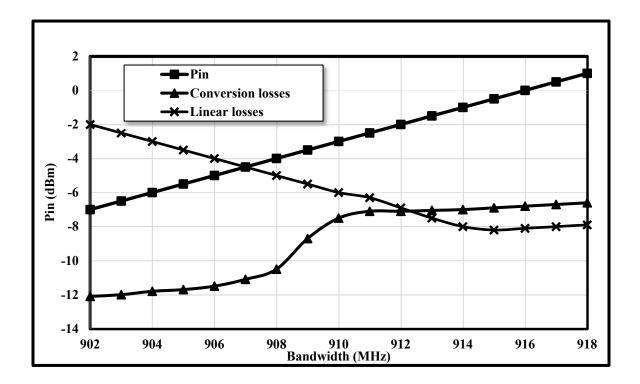

| 4.5  | The Simulation Results for the Optimized Class-F ET PA      | 132  |

| 4.6  | Power and Efficiency of ET PA using MATLAB as Behaviour     | ral  |

|      | Modelling                                                   | 135  |

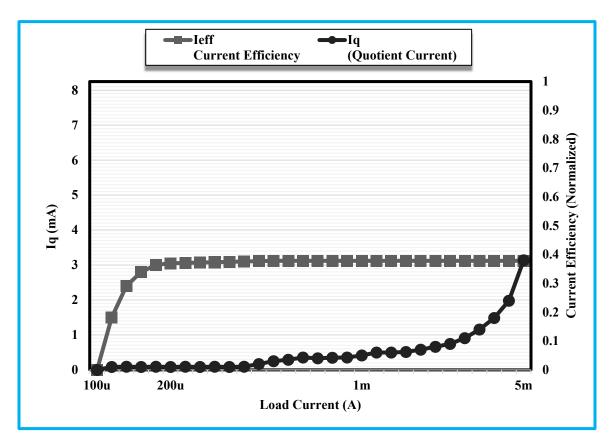

|      | 4.6.1 Current Efficiency vs the Current at the Output Load  | 139  |

| 4.7  | Comparison of Performance Parameters of the Proposed ULP    | ΕT   |

|      | PA with Current State-of-the-Art PAs for IEEE 802.11ah Stan | dard |

|      |                                                             | 140  |

| 4.8  | Cost Projection Analysis for Proposed ULP ET-PA             | 143  |

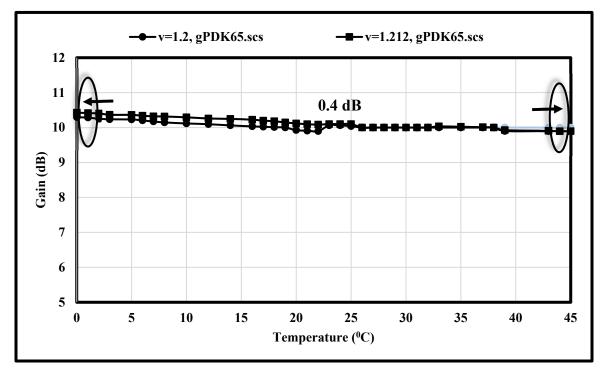

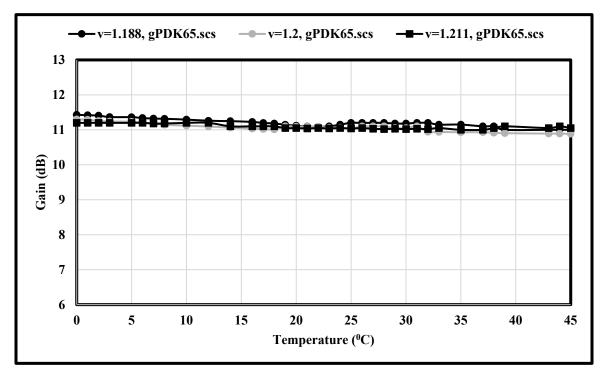

| 4.9  | Process-Voltage-Temperature (PVT) Variations for Simulation | n    |

|      | Results                                                     | 144  |

| 4.10 | Conclusion                                                  | 146  |

| DISC | CUSSION AND CONCLUSION                                      | 148  |

| 5.1  | Implications of the Study                                   | 148  |

| 5.2  | Summary of Contribution and Practical Implications of Study | 148  |

| 5.3  | Limitations of the Research                                 | 150  |

| 5.4  | Future Perspective                                          | 151  |

|      | 5.4.1 Energy Harvesting Integration                         | 151  |

|      | 5.4.2 Machine Learning and Cognitive Radio                  | 151  |

|      | 5.4.3 5G and Beyond                                         | 152  |

|      | 5.4.4 Security and Trustworthiness                          | 152  |

|      | 5.4.5 Cross-disciplinary Collaboration                      | 152  |

| 5.5  | Sustainable Development Goals (SDGs) Mapped with this       |      |

|      | Research                                                    | 153  |

5

| REFERENCES |                                                    | 156 |

|------------|----------------------------------------------------|-----|

| 5.7        | Conclusion                                         | 154 |

| 57         |                                                    | 154 |

| 5.6        | Artificial Intelligence (AI) and CMOS RF PA Design | 153 |

## LIST OF TABLES

| TABLE NO   | D. TITLE                                                      | PAGE |

|------------|---------------------------------------------------------------|------|

| Table 2.1: | Nomenclature of IEEE low power frequency standards [56]       | 19   |

| Table 2.2: | Comparison of various classes of PA [74]                      | 27   |

| Table 2.3: | Performance evaluation of various classification of supply    |      |

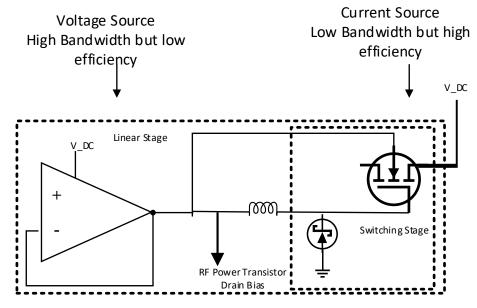

|            | modulators                                                    | 49   |

| Table 2.4: | Detail comparison of linear and switching ET supply modulator |      |

|            | (regulator) variant design [75]                               | 52   |

| Table 2.5: | Comparison of popular modern PA design techniques             | 54   |

|            |                                                               |      |

| Table 4.1: | Comparison of the proposed ULP DPA performance to state-of-   |      |

|            | the-art PA designs [146]                                      | 129  |

| Table 4.2: | Comparison of the proposed ULP ET PA performance to state-    |      |

|            | of-the-art PA designs using 65-nm CMOS Technology             | 141  |

## **LIST OF FIGURES**

| FIGURE NO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TITLE                                                           | PAGE |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------|

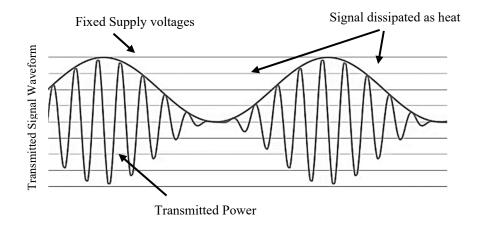

| Figure 1.1: In                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | terpretation of Transmitted Power over Dissipated Power for     |      |

| RI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | F PA [32]                                                       | 4    |

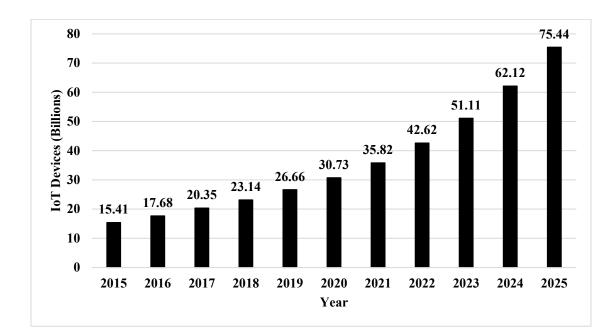

| Figure 1.2: Ez                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | xpected IoT-connected devices worldwide (in billions) by        |      |

| 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25 [33]                                                         | 5    |

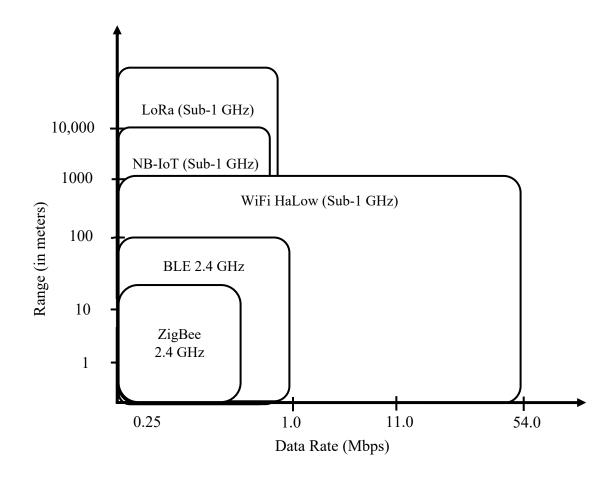

| Figure 2.1: Ez                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | xisting IEEE Low-power Standards: The WPAN and long-            |      |

| ra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | nge low-power WLAN technologies                                 | 18   |

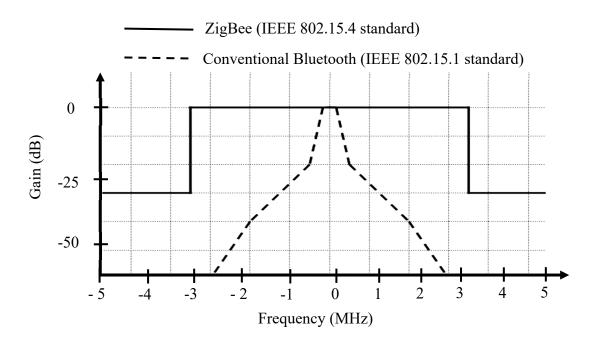

| Figure 2.2: Po                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ower Spectral Mask comparison of ZigBee and Bluetooth           |      |

| sta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | andards [59]                                                    | 22   |

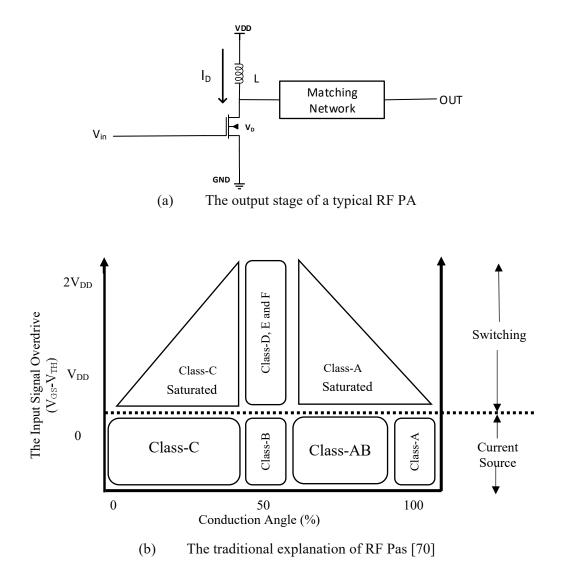

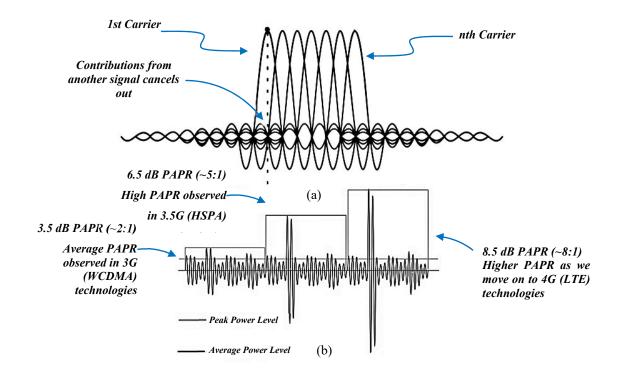

| Figure 2.3: (a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ) An RF PA output stage in a simplified form (b) Traditional    |      |

| ex                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | planations of RF PAs.                                           | 25   |

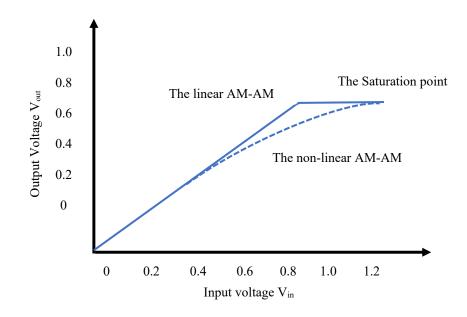

| Figure 2.4: G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ain compression and the impact of linearization are seen on a   |      |

| PA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | A gain plot [79]                                                | 29   |

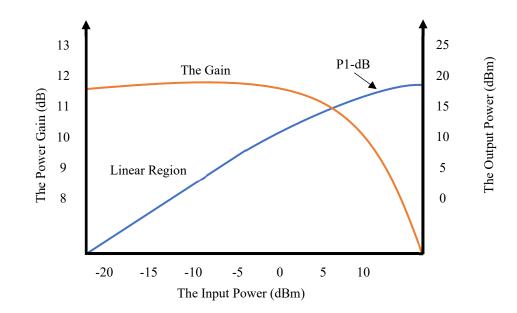

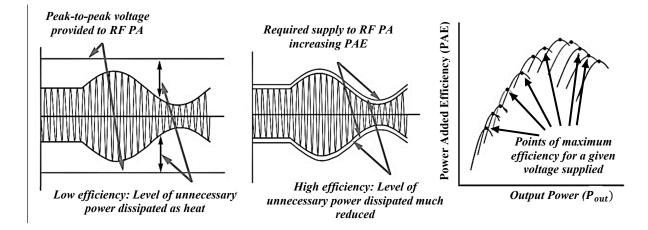

| Figure 2.5: The second | he Power Gain (dB), The Output Power (dBm) over the Input       |      |

| Pc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ower (dBm) [81]                                                 | 31   |

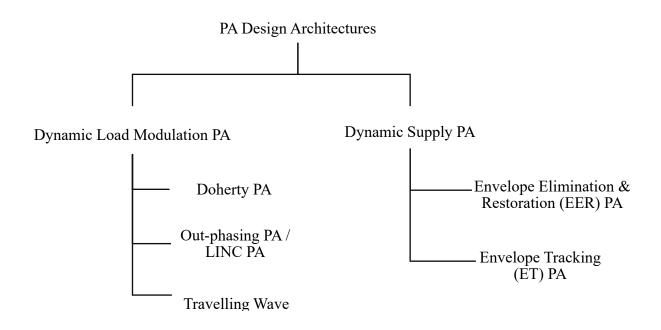

| Figure 2.6: M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | odern Trends in PA design architectures                         | 32   |

| Figure 2.7: R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | F PA Research Trends [75]                                       | 33   |

| Figure 2.8: (a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ) The traditional DPA concept and (b) the OBO efficiency        | 35   |

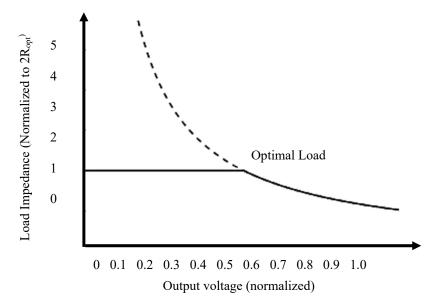

| Figure 2.9: D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PA optimum load-impedance for both ideal and real               |      |

| со                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | mponent design                                                  | 35   |

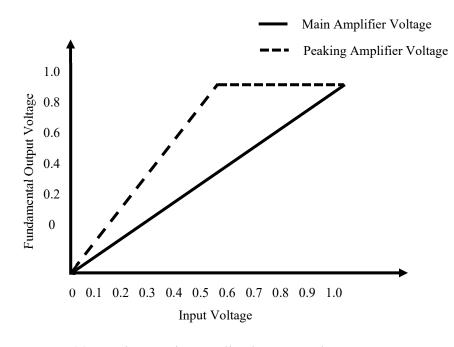

| Figure 2.10: I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Fundamental normalized (a) output voltage and (b) output        |      |

| cu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | rrent for main and peaking amplifiers over fundamental input    |      |

| VO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ltages (c) the peak efficiency that is reached at the OBO level |      |

| γ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 37                                                              |      |

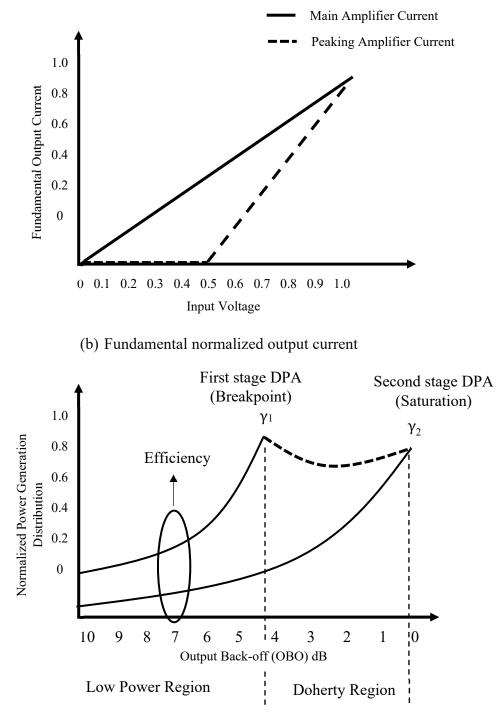

| Figure 2.11: The out-phasing PA Architecture [96]                                | 42 |

|----------------------------------------------------------------------------------|----|

| Figure 2.12: Traditional EER Architecture [21]                                   | 43 |

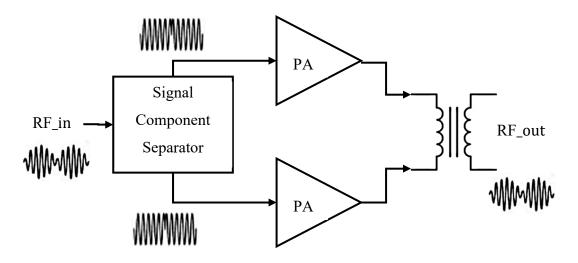

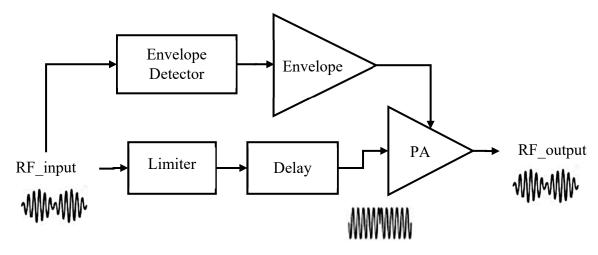

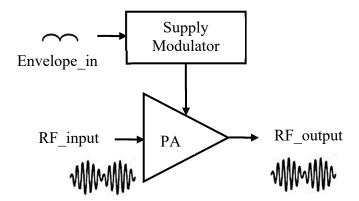

| Figure 2.13: Representation of the simplified ET architecture                    | 44 |

| Figure 2.14: Conventional ET architecture with high knee voltage supply          |    |

| modulator design [103]                                                           | 45 |

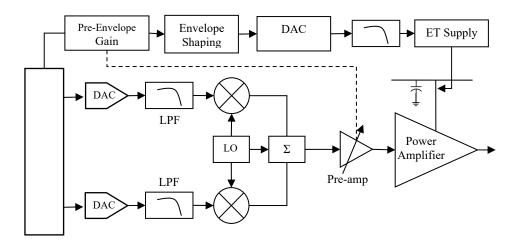

| Figure 2.15: (a) Conventional two-stage ET supply architecture with linear       |    |

| and switching stages for RF PA is simplified (b) ET PA system                    |    |

| using an ED to deliver the envelope signal.                                      | 47 |

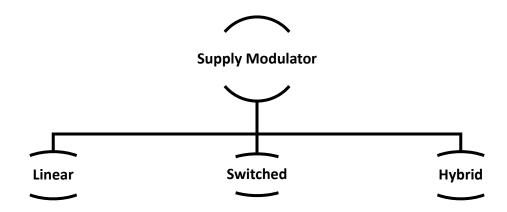

| Figure 2.16: Categories of supply modulators for ET-PA                           | 48 |

| Figure 2.17: The first time a MOS transistor was measured at a very low          |    |

| current (results from Vittoz's notebook) [123, 124]                              | 57 |

| Figure 2.18: Subthreshold and super threshold regions of operation               | 59 |

| Figure 2.19: The over-drive voltage (Vov) and the drain-source voltage           |    |

| $(V_{DS})$ , with respect to inversion coefficient [127].                        | 61 |

| Figure 2.20: The $g_m/I_D$ curve for two $V_{DS}$ values as simulated using      |    |

| nanoscale CMOS technology [127]                                                  | 65 |

| Figure 3.1: DPA representation with $\lambda/4$ Impedance inverter [140]         | 71 |

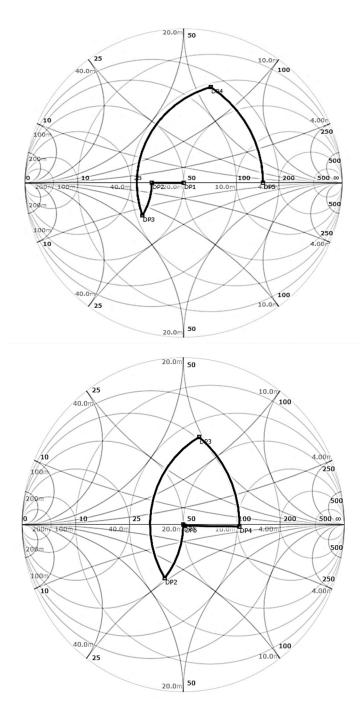

| Figure 3.2: (a) Equivalent RLC circuit model and (b) Impedance matching          |    |

| using the Smith chart for the lumped parameters of the power                     |    |

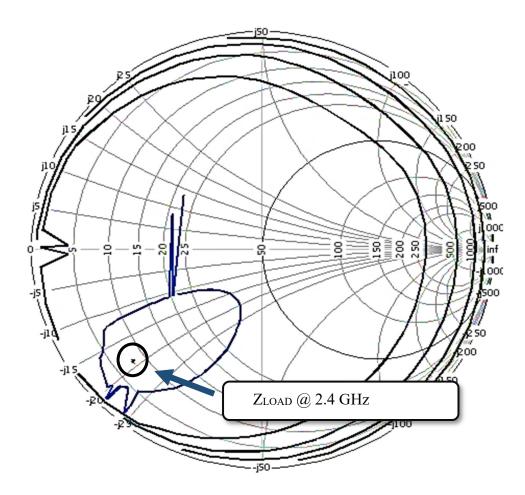

| combiner and divider models [146]                                                | 74 |

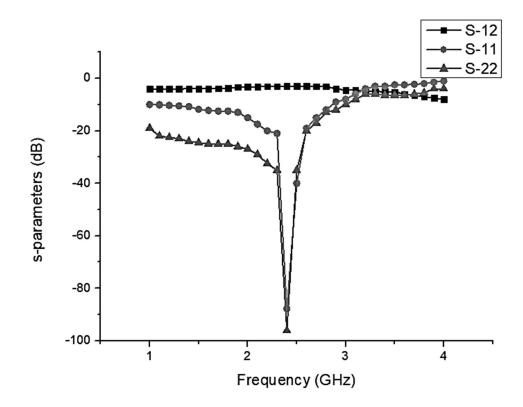

| Figure 3.3: Input return loss (S11), insertion loss (S12) and output return loss |    |

| (S <sub>22</sub> ) for power divider ideal circuit model                         | 76 |

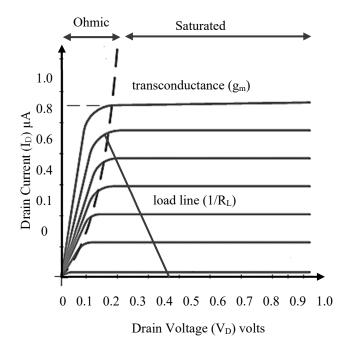

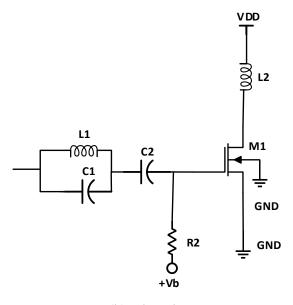

| Figure 3.4: (a) DC-plot of nonlinear parameters generated by simulation          |    |

| model and load line captured for class-B biased at less than                     |    |

| threshold values. (b) The Class-B PA using Ideal discrete                        |    |

| components (Analog Library) across M1 (65-nm RF-nMOS                             |    |

| library)                                                                         | 78 |

| Figure 3.5: The DPA architecture using ideal non-linear analogue library         |    |

| components ignoring the parasitic and channel length                             |    |

| modulation effects                                                               | 80 |

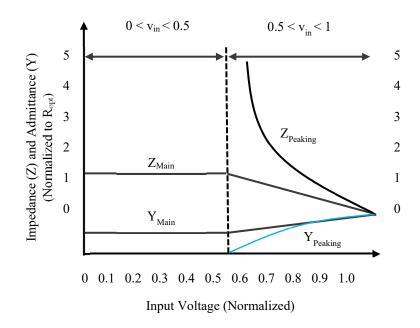

| Figure 3.6: Impedance and admittance trend for both the main and peaking  |     |  |

|---------------------------------------------------------------------------|-----|--|

| amplifiers with respect to the input voltage (normalized)                 | 82  |  |

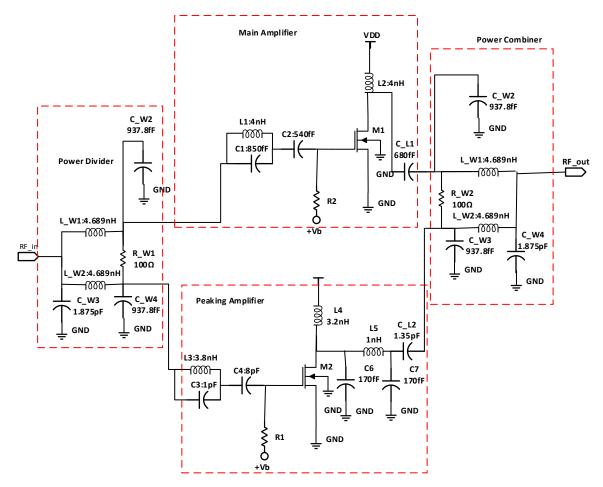

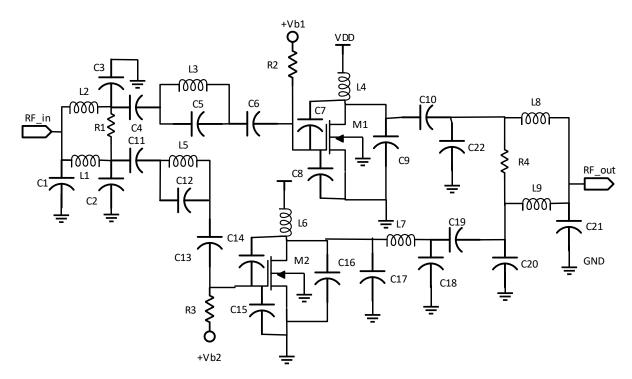

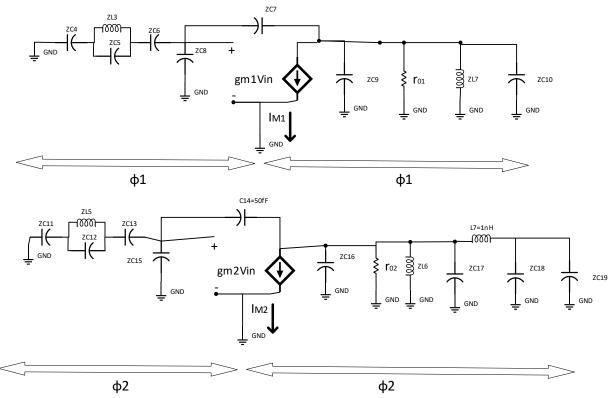

| Figure 3.7: Proposed ULP DPA using 65-nm CMOS Technology [146]            | 83  |  |

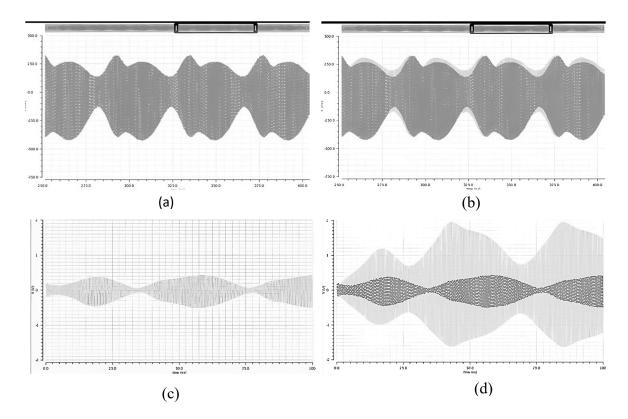

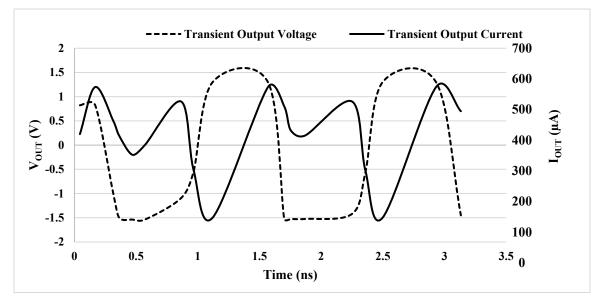

| Figure 3.8: The transient state impact (a) before inter-stage capacitance |     |  |