Muhammad Umair Arif

01-244222-014

# RESOURCE OPTIMIZE FPGA IMPLEMENTATION OF SONAR System

Master of science in Electrical Engineering

Supervisor: Dr Junaid Imtiaz

Co-Supervisor: Asim Altaf Shah

Department of Electrical Engineering Bahria University Islamabad

MS - 13 Thesis Completion Certificate

Student Name: **Muhammad Umair Arif** Registration Number: **58575** Program of Study: **Masters of Science in Electrical Engineering** Thesis Title: **Implementation of Linear array signal processing of FPGA in signal domain**

It is to certify that the above student's thesis has been completed to my satisfaction and, to my belief, its standard is appropriate for submission for evaluation. I have also conducted plagiarism test of this thesis using HEC prescribed software and found similarity index at **12%** that is within the permissible set by the HEC. For MS/MPhil/PhD. I have also found the thesis in a format recognized by the BU for MS/MPhil/PhD thesis.

Principle Supervisor's Signature: Principle Supervisor's Name: September 1, 2024

MS - 14 A Author's Declaration

I, **Muhammad Umair Arif** hereby state that my MS thesis titled **"Implementation of Linear array signal processing of FPGA in signal domain"** is my own work and has not been submitted previously by me for taking any degree from **"Bahria University, Islamabad"** or anywhere else in the country / world.

At any time if my statement is found to be incorrect even after my Graduate the university has the right to withdraw cancel my MS degree.

Muhammad Umair Arif 01-244222-014 September 1, 2024

page-3 of.82

MS - 14B Plagiarism Undertaking

# I, Muhammad Umair Arif solemnly declare that research work presented in the thesis titled Implementation of Linear array signal processing of FPGA in signal domain

is solely my research work with no significant contribution from any other person. Small contribution / help whenever taken has been duly acknowledged and that complete thesis has been written by me.

I understand the zero tolerance policy of Bahria University and the Higher Education Commission of Pakistan towards plagiarism. Therefore, I as an author of the above titled thesis declare that no portion of my thesis has been plagiarized and any material used is properly referred / cited.

I undertake that if I am found guilty of any formal plagiarism in the above titled thesis even after award of MS degree, the university reserves the right to withdraw / revoke my MS degree and HEC and the university has the right to publish my name on HEC / University Website on which name of students who submitted plagiarized thesis are placed.

Muhammad Umair Arif

01-244222-014 August 28, 2024

# Acknowledgments

I must first and foremost express my deepest gratitude to my advisor, Mr Asim Altaf Shah for his unyielding support, guidance, and motivation throughout this process. Their invaluable insights and expertise has moulded this thesis into its current form.

I would like to thank my thesis committee Dr Junaid Imtiaz, Dr Atif Jafri, for their invaluable feedback, advice and time. We would like to acknowledge that their perspective significantly enriched this work.

I extend my sincere thanks to the lab caretaker and staff. This supportive environment was essential for the progression of my research.

Finally, I am grateful to my family, My parents for unconditional support and constant encouragement in everything I do.

This thesis is a reflection of the effort and support from all those amazing people Thanks, everyone you were a part of the journey.

Muhammad Umair Arif

# Acronyms and Abbreviations

| FPGA  | Field Programmable gate arrays |

|-------|--------------------------------|

| Sonar | Sound Navigation and Ranging   |

| DSP   | Digital Signal Processing      |

| FFT   | Fast Fourier Transform         |

| IFFT  | Inverse Fast Fourier Transform |

| SP    | Signal Processing              |

| IP    | Intellectual properties        |

page-6 of.82

# ABSTRACT

Field Programmable Gate Array (FPGA) is an efficient and compact tool for fast processing and computations of signals. In this project, we explore the capabilities of Sonar system implemented on FPGA, addressing the processing time to be minimize. Sonar technology is crucial for underwater target recognition, detection and also for other liabilities like, to check and measure the underwater crimes. Typically, Sonar system rely on hydrophones for reliable processing. In this project, we are implementing the 6-channel linear array beamforming on FPGA. From each channel, data of 2048 samples were fed into the model for processing. The process begins with the application of a Fast Fourier Transform of the input data. The resulting FFT data is then subjected to beamforming, where desired frequency bins of the FFT result are multiplied by prestored coefficients in a ROM. Finally, we take the Inverse Fast Fourier Transform to take the signal back into its original shape. We analyze the results by comparing it with the Matlab fix model benchmark. Our primary objective is the implementation of this linear beamforming on FPGA utilizing minimum Hardware resources. The system successfully meets the stringent requirement of processing the entire algorithm in under 2 milliseconds. The implementation was carried out using the Verilog hardware description language, ensuring an optimized and reliable solution for real-time sonar signal processing.

# **Table of Contents**

| THESIS COMPLETION CERTIFICATE             | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AUTHOR DECLARATION                        | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PLAGIARISM UNDERTAKING                    | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ACKNOWLEDGEMENTS                          | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ACRONYMS AND ABBREVIATIONS                | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ABSTRACT                                  | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CHAPTER 1                                 | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| INTRODUCTION                              | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1.1 Project background                    | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1.2 Project Description                   | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1.3 Project Objective                     | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CHAPTER 2                                 | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| LITERATURE REVIEW                         | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.1 Introduction                          | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.1.1 Scope of the review                 | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.2 Planar Array signal Processing        | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.2.1 Introduction                        | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.2.2 A review of Sonar array limitations | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.2.3 Areas of Working                    | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.3 Overview of Sonar Technology          | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.3.1 History of Sonar Technology         | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.3.2 Types of Sonar System               | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.3.3 Different Sonar Principle           | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                           | AUTHOR DECLARATION<br>PLAGIARISM UNDERTAKING<br>ACKNOWLEDGEMENTS<br>ACRONYMS AND ABBREVIATIONS<br>ABSTRACT<br>CHAPTER 1<br>INTRODUCTION<br>1.1 Project background<br>1.2 Project Description<br>1.3 Project Objective<br>CHAPTER 2<br>LITERATURE REVIEW<br>2.1 Introduction<br>2.1.1 Scope of the review<br>2.2 Planar Array signal Processing<br>2.2.1 Introduction<br>2.2.2 A review of Sonar array limitations<br>2.3.3 Areas of Working<br>2.3.1 History of Sonar Technology<br>2.3.1 History of Sonar Technology<br>2.3.2 Types of Sonar System |

## Resource Optimize FPGA Implementation of Sonar System

|   | 2.3.4 Application of Sonar Technology                                                | 24 |

|---|--------------------------------------------------------------------------------------|----|

|   | 2.4 Fundemantals of FPGA Technology                                                  | 26 |

|   | 2.4.1 Advantages of FPGA-Based Prototyping in VLSI Design                            | 26 |

|   | 2.4.2 Leveraging FPGA Technology for Advanced Signal Processing                      | 26 |

|   | 2.5 Hardware descriptive language for FPGA                                           | 27 |

|   | 2.5.1 VHDL                                                                           | 27 |

|   | 2.5.2 Verilog                                                                        | 28 |

|   | 2.5.3 Comparison between Verilog and VHDL                                            | 28 |

|   | 2.6 Optimization techniques for FPGA implementation                                  | 29 |

|   | 2.6.1 Significance of Ping-Pong Buffers in FPGA Systems                              | 29 |

|   | 2.6.2 Optimization of Performance through decomposition                              | 30 |

|   | 2.6.3 Efficient Data Handling and Signal Processing in Underwater Using FPGA         | 30 |

|   | 2.7 Future trends and research directions                                            | 31 |

|   | 2.7.1: Enhancing Underwater Security: Challenges and Innovations in Sonar Technology | 31 |

|   | 2.7.2: The Role of Fractional Fourier Transform in Sonar Systems                     | 32 |

|   | 2.8 Existing Hardware Methods of Sonar System                                        | 32 |

|   | 2.8.1 ASICs                                                                          | 33 |

|   | 2.8.2 ASIPs                                                                          | 33 |

|   | 2.8.3 FPGAs                                                                          | 34 |

|   |                                                                                      |    |

| 3 | CHAPTER 3                                                                            | 36 |

|   | METHODOLOGY                                                                          | 36 |

|   | 3.1 Introduction                                                                     | 36 |

|   | 3.2 Conversion process of Matlab code                                                | 37 |

|   | 3.2.1 Implementation of Multi beam Sonar using FPGA                                  | 37 |

|   | 3.2.2 Matlab to Verilog Workflow                                                     | 38 |

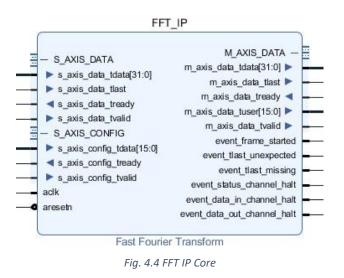

|   | 3.2.3 FFT processing using Xilinx IP and Verilog for efficient utilization           | 39 |

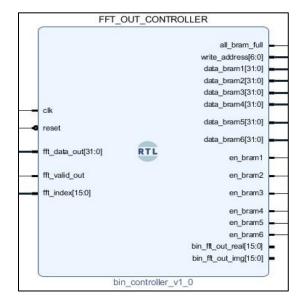

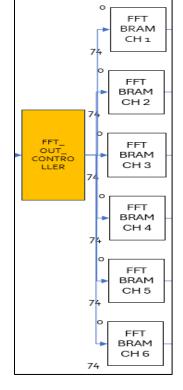

|   | 3.3 Selective FFT bin extraction and beamforming using Verilog                       | 41 |

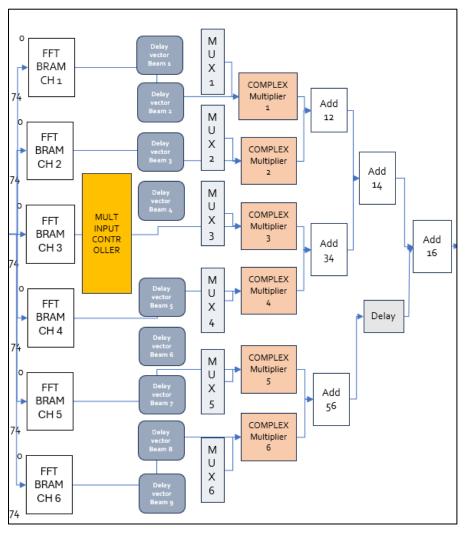

|   | 3.3.1 Sequential Beamforming with selective FFT bins using Verilog                   | 42 |

page-9 of.82

## Resource Optimize FPGA Implementation of Sonar System

| 4 | CHAPTER 4                                         | 43 |

|---|---------------------------------------------------|----|

|   | IMPLEMENTATION DETAILS                            | 43 |

|   | 4.1 Introduction                                  | 43 |

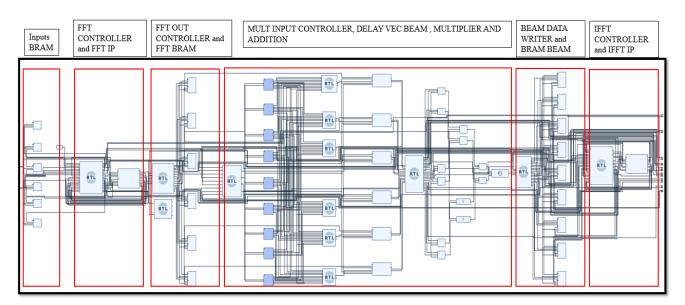

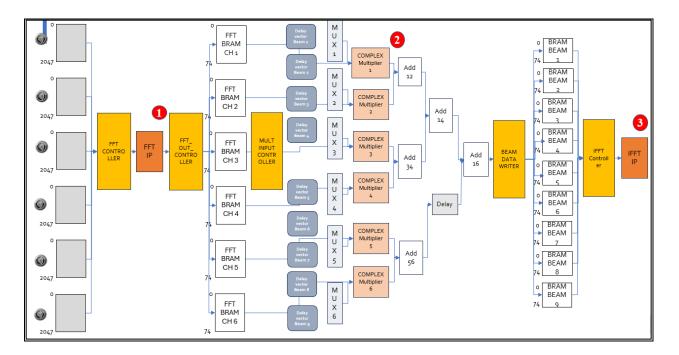

|   | 4.2 System Implementation                         | 44 |

|   | 4.2.1 Software Configuration                      | 44 |

|   | 4.2.2 FFT Integration                             | 46 |

|   | 4.3 Beamforming Implementation                    | 50 |

|   | 4.3.1 Implementation of Beamforming Algorithm     | 53 |

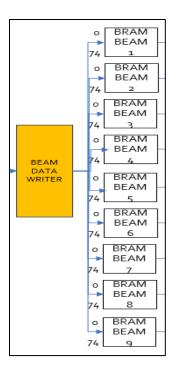

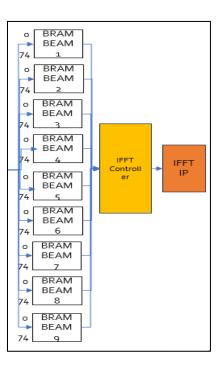

|   | 4.4 Inverse Fast Fourier Transform Implementation | 57 |

| _ |                                                   |    |

| 5 | CHAPTER 5                                         | 59 |

|   | EVALUATION RESULTS                                | 59 |

|   | 5.1 Results                                       | 59 |

|   | 5.2 Resource Utilization                          | 75 |

|   | 5.2.1 Comparison                                  | 75 |

| 6 | CHAPTER 6                                         | 78 |

|   | CONCLUSION                                        | 78 |

|   |                                                   |    |

| 7 | CHAPTER 7                                         | 80 |

|   | REFERENCES                                        | 80 |

# **List of Figures**

| FIG. 2.1 SENSORS DEPLOYMENT                                      |                              |

|------------------------------------------------------------------|------------------------------|

| FIG. 2.2 ARRAY SIGNAL FIELD                                      |                              |

| FIG. 2.3 OPERATING PRINCIPLE OF SONAR                            | 25                           |

| FIG. 3.1 MATLAB MODEL                                            |                              |

| FIG. 4.1 VERILOG CODE BLOCK DIAGRAM                              | 44                           |

| FIG. 4.2 DATA FLOW                                               |                              |

| FIG. 4.3 FFT CONTROLLER                                          | 46                           |

| FIG. 4.4 FFT IP CORE                                             |                              |

| FIG. 4.5 FFT IP CORE SETTINGS                                    |                              |

| FIG. 4.6 FFT IP CORE SETTING 2.                                  |                              |

| FIG. 4.7 RESOURCES SUMMARY WITH BIT REVERSED ORDER.              | 49                           |

| FIG. 4.8 IMPLEMENTATION DETAILS.                                 |                              |

| FIG. 4.9 FFT_OUT_CONTROLLER TO BRAMS                             | ERROR! BOOKMARK NOT DEFINED. |

| FIG. 4.10 FFT_OUT_CONTROLLER                                     |                              |

| Fig. 4.11 FFT_BRAM IP                                            |                              |

| FIG. 4.12 BLOCK RAM IP DETAIL 1                                  | 53                           |

| FIG. 4.13 BLOCK RAM IP DETAIL 2                                  | 53                           |

| FIG. 4.14 BEAM FORMATION                                         |                              |

| FIG. 4.15 BEAM DATA WRITER                                       | 56                           |

| FIG. 4.16 IFFT CONTROLLER                                        |                              |

| FIG. 4.17 BLOCK DESIGN MODEL                                     |                              |

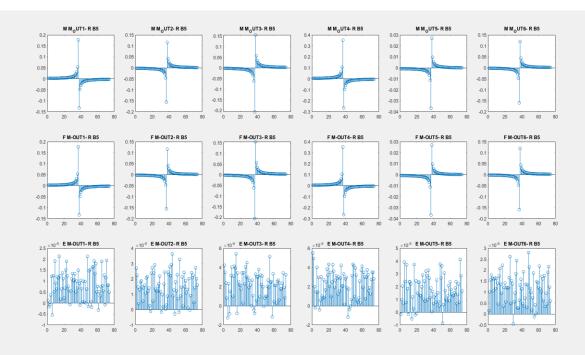

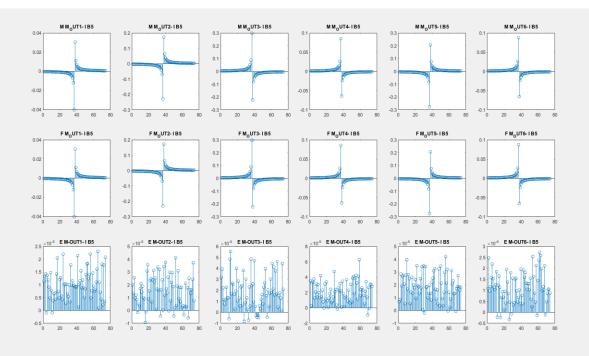

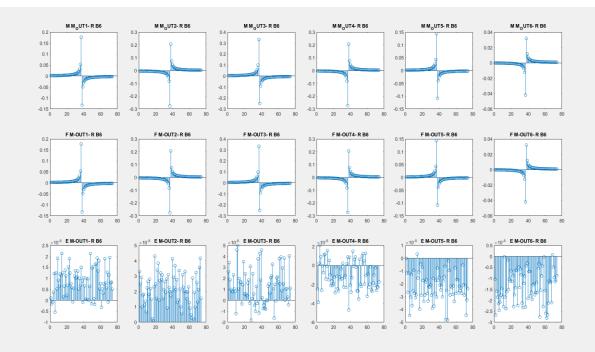

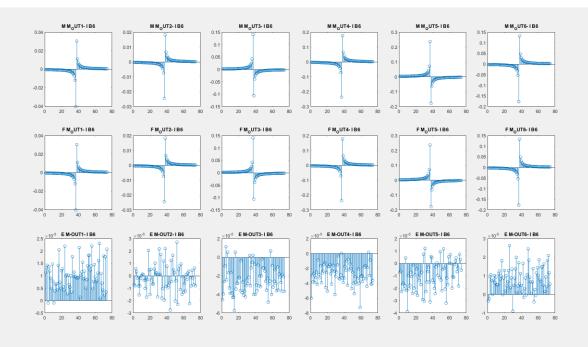

| FIG. 5.1 RESULT COMPARISON STAGES                                |                              |

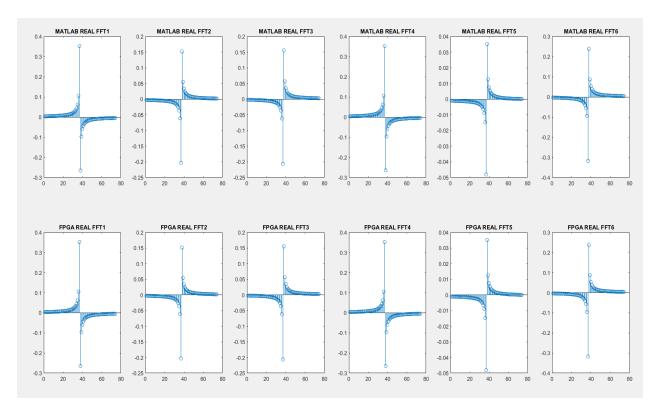

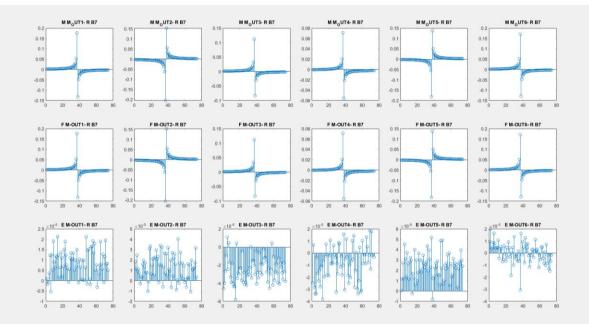

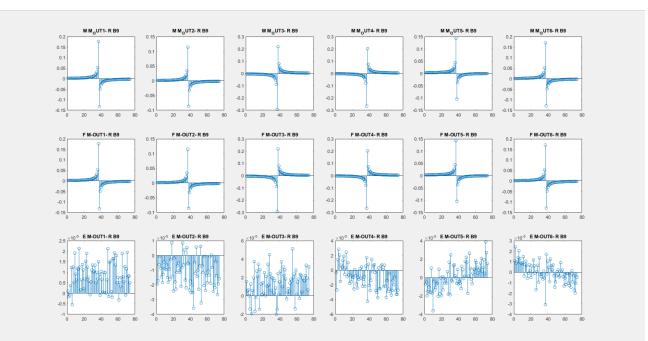

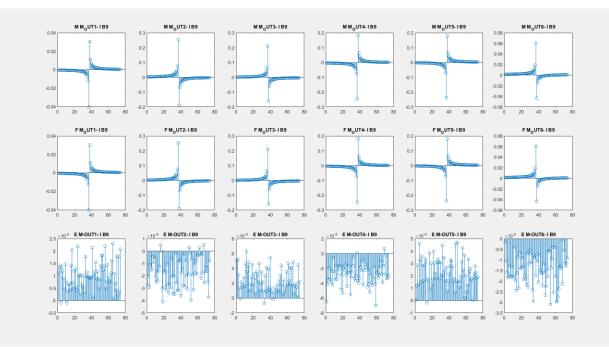

| FIG. 5.2 FFT OUTPUT RESULT COMPARISON (REAL VALUES)              |                              |

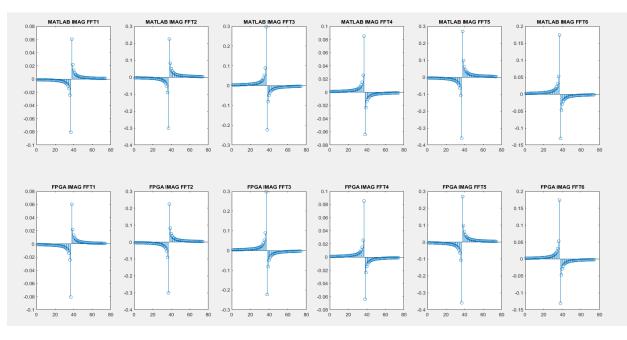

| FIG. 5.3 FFT OUTPUT RESULT COMPARISON (IMAGINARY VALUES)         |                              |

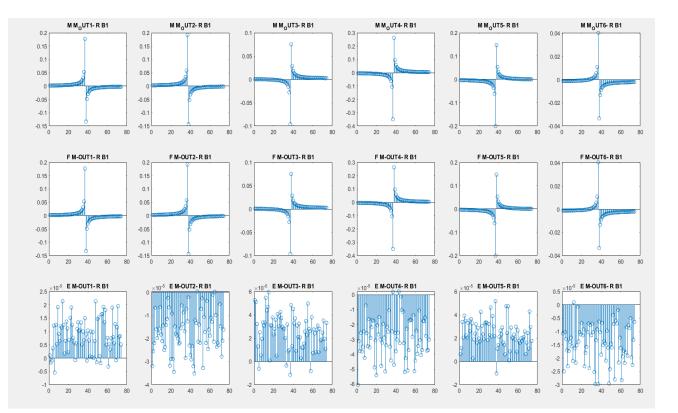

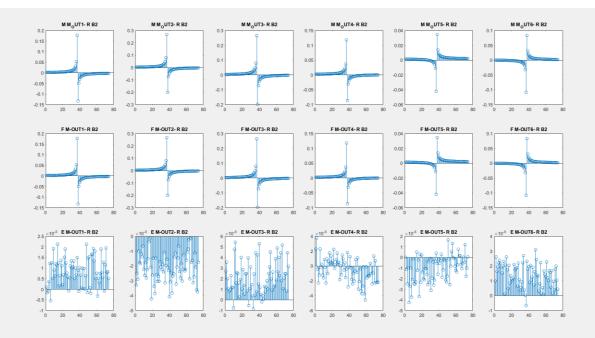

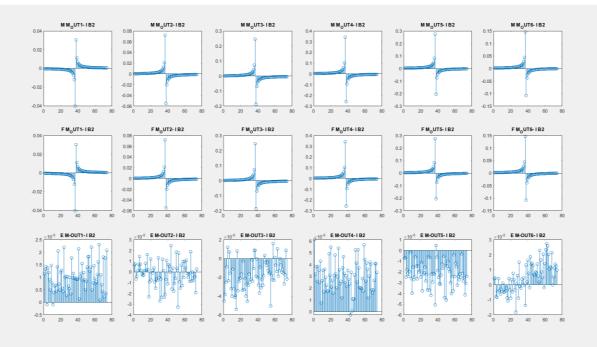

| FIG. 5.4 MULTIPLICATION RESULTS COMPARISON REAL OF BEAM1         |                              |

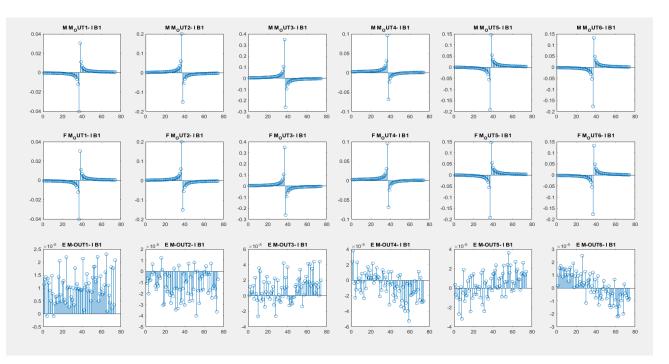

| FIG. 5.5 MULTIPLICATIONS RESULTS COMPARISON IMAGINARY OF BEAM1   | 63                           |

| FIG.5.6 MULTIPLICATIONS RESULT COMPARISON REAL OF BEAM2          |                              |

| FIG. 5.7 MULTIPLICATIONS RESULT COMPARISON IMAGINARY OF BEAM2    |                              |

| FIG. 5.8 MULTIPLICATIONS RESULT COMPARISON REAL OF BEAM 3        |                              |

| FIG. 5.9 MULTIPLICATIONS RESULT COMPARISON IMAGINARY OF BEAM3    |                              |

| FIG. 5.10 MULTIPLICATIONS RESULT COMPARISON REAL OF BEAM 5       |                              |

| FIG. 5.11 MULTIPLICATIONS RESULT COMPARISON IMAGINARY OF BEAM 5  |                              |

| FIG. 5.12 MULTIPLICATIONS RESULT COMPARISON REAL OF BEAM 6       |                              |

| FIG.E 5.13 MULTIPLICATIONS RESULT COMPARISON IMAGINARY OF BEAM 6 |                              |

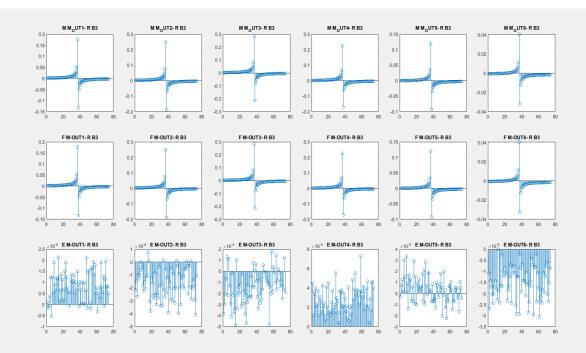

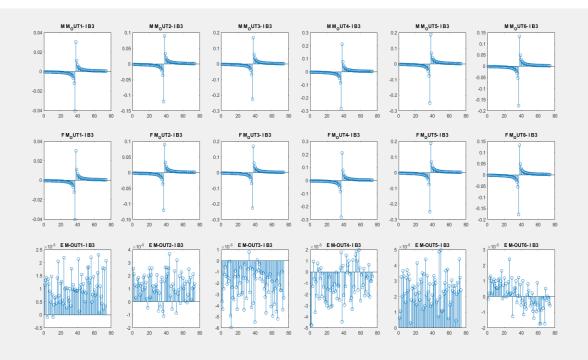

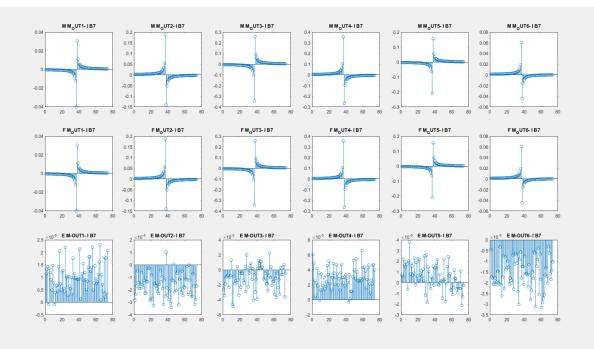

| FIG. 5.14 MULTIPLICATIONS RESULT COMPARISON REAL OF BEAM 7       | 67                           |

| FIG. 5.15 MULTIPLICATIONS RESULT COMPARISON IMAGINARY OF BEAM 7  | 68                           |

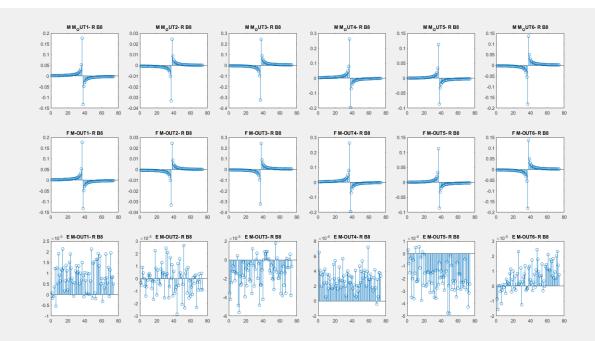

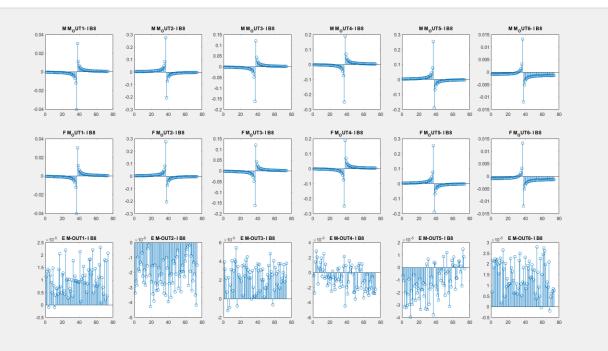

| FIG. 5.16 MULTIPLICATIONS RESULT COMPARISON REAL OF BEAM 8       | 68                           |

| FIG. 5.17 MULTIPLICATIONS RESULT COMPARISON IMAGINARY OF BEAM 8  |                              |

| FIG. 5.18 MULTIPLICATIONS RESULT COMPARISON REAL OF BEAM 9       |                              |

| FIG. 5.19 MULTIPLICATIONS RESULT COMPARISON IMAGINARY OF BEAM 9  | 70                           |

page-11 of.82

## Resource Optimize FPGA Implementation of Sonar System

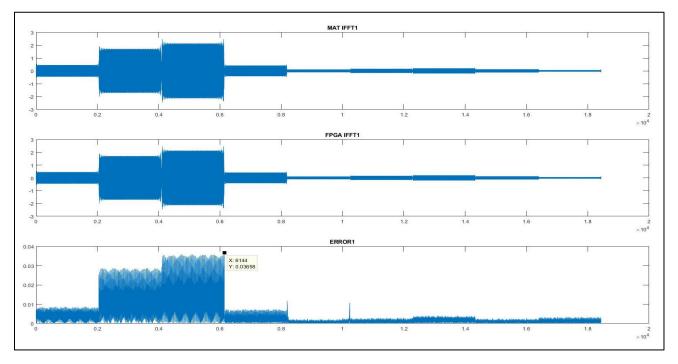

| FIG. 5.20 IFFT RESULTS COMPARISON IFFT: MATLAB VS FPGA                 | 70 |

|------------------------------------------------------------------------|----|

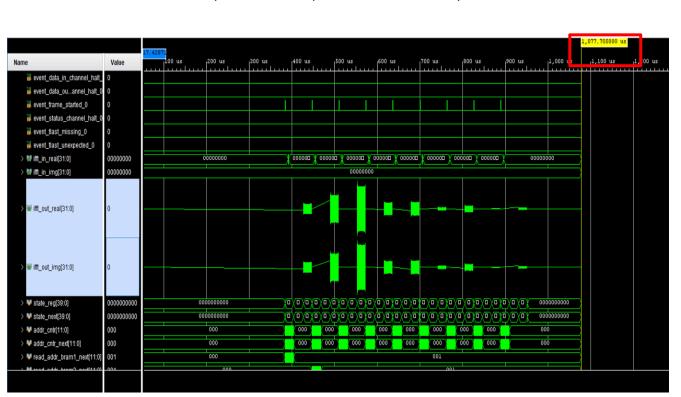

| FIG. 5.21 TIMING OF PROCESS SHOWING IFFT RESULT OF LAST BEAM RECEIVED. | 72 |

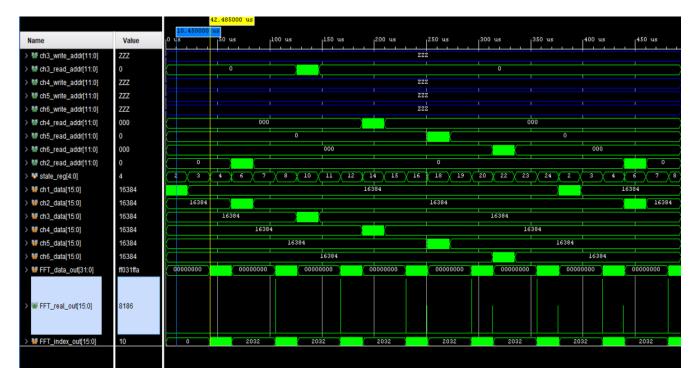

| Fig. 5.22 FFT results of all 6 channels                                | 73 |

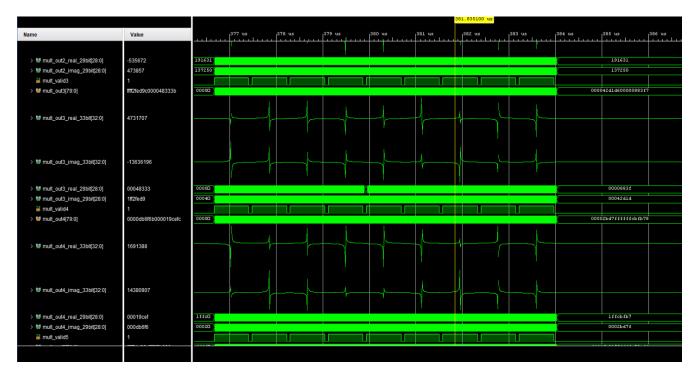

| FIG. 5.23 MULTIPLICATION RESULTS MULT1 AND MULT2                       | 73 |

| FIG. 5.24 MULTIPLICATION RESULTS MULT3 AND MULT4                       | 74 |

| FIG. 5.25 MULTIPLICATION RESULT MULT5 AND MULT6                        | 74 |

# List of Table

| TABLE 1 UTILIZED RESOURCES IN RESEARCH    76   | , |

|------------------------------------------------|---|

| TABLE 2 RESOURCES UTILIZED IN PRIOR WORK    77 | , |

page-13 of.82

## **CHAPTER 1**

# **INTRODUCTION**

#### 1.1: Project Background

The development of digital virtual systems is constantly replacing analog systems. Digital systems are the true strength of current-day corporations, products, techniques, and services, and their characteristics are increasingly enhanced by these technologies. Communication, traffic, control, weather forecasting systems, internet and so forth Programmable Gate Array (FPGA) devices are the applications of present-day digital technologies. These devices (FPGAs) operate at high clock frequencies and attain high execution in computations of digital and signal processing (DSP) algorithms. Sonar (also known as sound navigation and ranging) is a technique that uses sound propagation to navigate and measure distances for objects and targets. We required results in minimum time to quickly analyze and respond accordingly. FPGAs are best solutions to keep track of fast signal processing and having the functionalities capable to work efficiently in these conditions. Now modeling of these algorithms in a way to get the result with using minimum resources and in less time is the challenge and the target. The thesis focuses on the implementation of a 6-channel linear array beamforming system for SONAR, utilizing FPGA technology and

page-14 of.82

programmed in Verilog HDL. The project involves critical signal processing algorithms, including FFT, IFFT, and beamforming, implemented on FPGA to achieve real-time processing. Beamforming is optimized using nine azimuth angles for directing acoustic signals and enhancing detection accuracy. The system is designed to handle 444 coefficients per beam and employs ROM-based storage and multiplexing techniques to select beams for processing.

#### **1.2: Project Description**

In this project, data is received from six different channels, organized in a linear array format, enabling target detection and analysis in one dimension. The project is divided into three primary stages. The first stage involves applying a 2048-point FFT to the data from each of the six channels. This transformation converts the time-domain signals into the frequency domain for further processing. In the second stage, beamforming is performed. This involves multiplying specific frequency bins, corresponding to the 38 kHz - 42 kHz range, by pre-determined coefficients. The system generates nine distinct beams, each with its own set of coefficients. The final stage is the baseband processing. Here, the results from the beamforming stage are processed using an Inverse Fast Fourier Transform (IFFT) to convert the data back into the time domain. Before applying the IFFT, the sample length is extended from 74 to 2048 to match the original FFT length. The entire computation process takes 1.07 milliseconds. The total number of clock cycles required for the operation is determined by the input frequency, which is 112,000 samples per second. FPGA's parallel processing capabilities are utilized to handle large data sets in real time, ensuring efficient

page-15 of.82

processing within the given 10 ms time frame. The system's accuracy and performance are verified by comparing the FPGA results with MATLAB simulations, demonstrating the potential of FPGA for scalable and high-performance SONAR applications.

## 1.3: Project Objective

This project focuses on developing and evaluating efficient low-complexity FPGA implementation of the Sonar system. The project aims to achieve efficient signal processing by integrating key algorithms such as FFT, IFFT, and beamforming, optimized for multiple azimuth angles. The goal is to leverage FPGA's parallel processing capabilities to handle large data sets and real-time computations, ensuring high-speed and accurate detection. The performance will be validated by comparing the results with MATLAB simulations, demonstrating FPGA's effectiveness in advanced SONAR systems. DSPs and GPP also provide fast results, but they take more hardware resources for operations like beam-forming. We are using VERILOG language for the implementation of the project. VIVADO is the software we use for project designing and to simulate the simulation. For the reference model, we use MATLAB to verify our Vivado design results.

# **CHAPTER 2**

# LITERATURE REVIEW

### 2.1 Introduction

#### 2.1.1 Scope of the review

We began by introducing planar array signal processing techniques, along with the operational environment necessary for their effective implementation. Signal processing in sonar systems can be broadly classified into two types: active and passive processing. Following this, we discussed the challenges encountered during sonar operation, such as the need for real-time processing, handling large volumes of data, and minimizing latency. These challenges necessitate a thorough investigation to optimize system performance. We then elaborated on why Field Programmable Gate Arrays (FPGAs) offer a superior solution compared to Digital Signal Processors (DSPs). FPGAs provide significant advantages, including reduced processing time and higher resource efficiency. This is due to their parallel processing capabilities and the ability to customize hardware configurations for specific tasks, making them ideal for real-time signal processing in sonar systems. Moreover, we discussed various optimization techniques that can be leveraged through the use of FPGAs to enhance the efficiency of our solution. These techniques include pipelining, parallelism, and efficient memory management, all of which contribute to lower latency and more effective use of hardware resources. We also explored future trends and emerging techniques that could lead to even more compact and efficient solutions for sonar signal processing. These advancements may include the integration of advanced algorithms and the continued evolution of FPGA technology, which could further enhance performance and reduce system size. Finally, we reviewed the Fast Fourier Transform (FFT) algorithm, its functionality, and its role in signal processing. We also touched on other relevant algorithms that contribute to the overall effectiveness of the sonar system. These algorithms are essential for transforming data between the time and frequency domains, which is a critical aspect of signal analysis in both active and passive sonar processing.

### 2.2 Planar Array Signal Processing

#### 2.2.1 Introduction

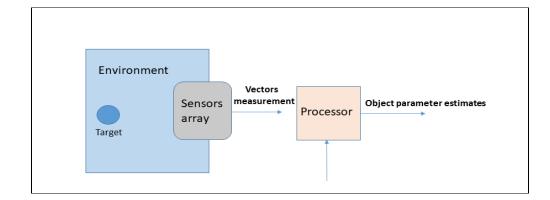

As the name indicates, "Planar Array Signal Processing" involves processing, data carrying signals collected from sensor arrays operating in the environment of interest (such as on the ground, above ground, or underwater). The relationship between the environment, sensor array,

and processor is illustrated in the system model in Fig 1. In passive array signal processing technology, the sensor array has the sole task of listening to the environment. In active sonar devices, emitters are used to illuminate the environment and sensor arrays listen for signals emitted from the environment and/or objects of interest [1]. Sensors can be used in many ways. Examples of sensors include:

- (a) Antennas in radar, radio communications, and radio astronomy

- (b) Hydrophones in sonar

- (c) Geophones in seismology

- (d) Ultrasonic probes and X- in medical imaging beam detectors.

2.2.2 A review of sonar array limitations

In radar, radio communications, and radio astronomy, antennas function as electronic devices designed to capture electromagnetic waves. In contrast, sonar, seismology, and medical imaging rely on sound transducers such as hydrophones, geophones, and ultrasound probes—that are engineered to respond to acoustic energy waves. Measurement vectors, collected by sensor arrays in discrete time intervals (snapshots), provide critical information about the environment and the target of interest, which may include details about the target's location, orientation, movement, or the number of sources (emitters) interacting with the sensor array. [9]

The processor's role is to generate accurate estimates of these parameters by extracting relevant information from the measurement vectors. However, the performance of the processing algorithms is constrained by several key factors. Firstly, sensor noise, which may be isotropic or anisotropic, affects the accuracy of the measurements. Secondly, inaccuracies in the mathematical modeling can arise when the assumed model fails to accurately represent the physical phenomena responsible for the sensor output.

Finally, the sensor's capacity to collect data is inherently limited by its size and the timebandwidth product of the event being measured. These limitations collectively impact the precision and reliability of signal processing in these applications.[1]

#### 2.2.3 Areas of working

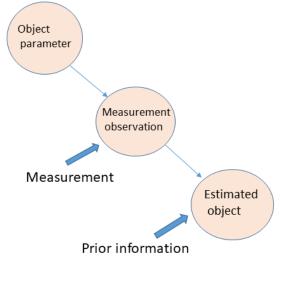

We have three areas in which we conceptualize the problems of array signal processing:

**Object Space**: The object space is characterized by a set of object parameters and environmental factors of interest, along with numerous other influencing elements. Specifically, the precise representation of the object's position is not directly known and must be inferred through the estimation of an unknown signal sequence function.

**Measurement (observation) area**: The measurement area is defined by two key factors: the specific types of light employed for environmental monitoring (relevant only to the operating system), and the data utilized for the specific design pattern structure of the retrieved collection. The data content within this space is consistently smaller than the corresponding physical space.

**Estimated position**: The third position in the conceptual model is defined by the estimated parameters that determine the position of the product. These parameter estimates, in essence, provide a solution to the array signal processing problem. [9]

Fig. 2.1 Array signal field

The arrays contains single-element transducers mounted in a way that improves signal directivity, increase the audio signal power level, improve beamforming, and aids in beam steering and shielding. The most common types of array are linear arrays, such as discrete and continuous elements, and planar arrays, which include circular, square, and rectangular arrays, each containing multiple transducer elements in different configurations. Although individual array elements are usually omnidirectional, the array itself can have multiple directions depending on its extension or surface.

## 2.3 Overview of Sonar Technology

#### 2.3.1 History of Sonar technology

Sonar technology has been developed over more than 100 years, with a long history of advancement and innovation in underwater acoustic technologies. The origins of sonar technology can be traced back to the nineteenth century, with significant progress made during the twentieth century, particularly during World War I and World War II where transducers finds an underwater applications, stands for Sound Navigation and ranging, encompasses both active and passive Sonar, driven by the need for underwater object detection and location.

The loss of the Titanic and submarine operation during World War I were important events that led to the advancement of sonar technology and highlighted the need for better underwater research [4]. The development of sonar and array technology continues with the increasing demand for purposes such as underwater research, hydrology, swimming, and fisheries research, including the exploitation of oil, gas and minerals.

#### 2.3.2 Types of Sonar System

**Passive Sonar:** The main purpose of Sonar is to navigate and locate objects underwater. In this echoes or sounds emitted by the objects and targets are listened and processed further. Passive systems can range from a single hydrophone to several hundred hydrophones arranged in various array geometries.

Active Sonar: We intentionally emits echoes and listened them once reflected back from the objects and then processed on the signals, extracting the information. [4]

#### 2.3.3 Different Sonar principles:

#### Single beam echo sounders:

SBES operates on the principle of transmitting and receiving updated products in the realms of hardware, firmware, and software. Specifically, sinusoidal pulses, synchronized by the master clock, are amplified by a power amplifier, where the sound power level is adjusted according to the water depth and carrier frequency. At the receiver, inputs are typically time-gated to prevent direct capture of the transmitted signal and to mitigate the effects of transmitter ringing. The signal then passes through a band-pass filter to eliminate ship noise. Finally, the signal is

processed via time-varied gain (TVG), with amplification based on the amplitude of the signal received at varying depths. [4]

#### Multi beam echo sounders:

MBES operates as a single beam with a small width and a small distance between each beam. The best MBES systems today have beam widths of  $0.5^{\circ}$  to  $1^{\circ}$  and can run more than 800 lines.

#### Side scan Sonar:

Side-scan sonar is a tool used to visualize the seabed and objects located on or above the seafloor. It employs a sonar generator and the movement of a transducer through the water to produce high-resolution, two-dimensional images of sonar patterns. The transducer can be mounted on the underside of the vessel's hull. A side-scan sonar system may feature a single sensor that emits an acoustic signal to the side of the platform, or it may have two sensors that emit acoustic signals on both sides of the platform, allowing for the scanning of a wide area of the seabed as the system moves forward through the water.

#### 2.3.4 Applications of Sonar Technology:

Seafloor mapping can also be used to search for wrecks of ships and airplanes. Sonar can also be used to locate lost items, such as cargo containers and other cargo on ships, or chemical weapons and war materiel, such as bombs and gas bombs. Marine geology uses sonar systems to identify, study, and map the seafloor, as well as to record sub-bottom profiles. This is often achieved using low-frequency parametric sonar. Additionally, underwater research that focuses on ambient noise, coral reef ecosystems, pollution from oil spills and waste dumping, and marine archaeology such as the search for historical artifacts and the study of submerged cities.

Fisheries research estimating fish species and fish biomass. Sonar systems also increase efficiency and catching operations.

Physical oceanography used to study various ocean phenomena resulting from small local temperature changes in shallow waters.

Fig. 2.2 Operating principle of Sonar

### 2.4 Fundamentals of FPGA Technology

#### 2.4.1 Advantages of FPGA-Based Prototyping in VLSI Design

Many procedures are involved in manufacturing integrated circuits form VLSI design. FPGA prototyping (Field Programmable Gate Array) is one of the procedure of them. Because of the importance of Simplicity, DSP hardware limitations, and FPGA customization for application-specific I/O requirements, FPGA-based systems offer six to twelve times the performance of traditional equivalent DSP systems. FPGA-based beam formers can provide computational power equivalent to multiple DSPs by leveraging symmetries in sensor arrays, enabling efficient broadcast of data to processing elements and pipelined operations for faster calculations. [13] The advantages of FPGAs, such as strong parallelism and the ability to handle high data rate algorithms, make them a suitable platform for real-time signal processing in high-frequency active sonar systems.

#### 2.4.2: Leveraging FPGA Technology for Advanced Signal Processing

FPGAs are instrumental in the heterogeneous integration of diverse "hard IP" blocks—such as SSDs and floating-point DSPs—enabling enhanced application-specific functionality. Recent advancements in FPGA technology, characterized by increased storage capacity, reduced power consumption, cost efficiency, and higher gate counts, have paved the way for high-performance

applications. These advancements allow FPGAs to parallelize algorithms efficiently, boosting power efficiency, flexibility, and accuracy, which are critical for SVM-based (Support Vector Machine) applications.[1]

In the context of digital beamforming, FPGA-based hardware implementations offer an efficient platform for deploying advanced algorithms and techniques such as Linearly Constrained Minimum Variance (LCMV) and Minimum Variance Distortion less Response (MVDR). When combined with a Quick-Support Vector Machine (QS-SVM) model for Direction of Arrival (DoA) estimation, these implementations ensure real-time execution with high throughput. The inherent parallelism and capability to handle high data rate algorithms make FPGAs an ideal choice for real-time signal processing in high-frequency active sonar systems. [13]

FPGAs facilitate the realization of complex algorithms in hardware, resulting in low latency and high data rates in practical applications. In signal processing, FPGA platforms decompose algorithms into various operations, such as multi-channel data demodulation, Fast Fourier Transform (FFT), beamforming, matched filtering, and Constant False Alarm Rate (CFAR) processing. These capabilities make FPGAs a powerful tool for executing sophisticated, realtime signal processing tasks in challenging environments.

#### 2.5: Hardware Description Language (HDL) for FPGA Programming

2.5.1 VHDL (Very large scale Hardware Description Language)

VHDL was developed as part of VHSIC (Very High Speed Integrated Circuit) in the 1980s under the auspices of the US Department of Defense. Standard language is ideal for describing complex processes. It also includes design support that makes managing large projects easier, allow the characteristics of combinational and sequential logics. VHDL is widely used in industries where reliability and stability are important, such as aerospace, defense and telecommunications.

#### 2.5.2: Verilog

Developed by Phil Moorby of Gateway Design Automation in the mid-1980s, Verilog has become one of the most popular HDLs due to its simplicity and ease of use. Verilog syntax is similar to the C programming language and can be used by engineers familiar with C. Verilog supports behavior and design, making it suitable for many levels of design abstraction. It includes design for modeling hardware components and connections. Verilog is widely used in the electronics, automotive and computers.

#### 2.5.3: Comparison of VHDL and Verilog

Both VHDL and Verilog support multiple levels of abstraction, including behavior, register transfer Level (RTL), and gate level. VHDL's powerful types and granularity make it ideal for large, complex models that require reliability. Verilog's simplicity and flexibility make it ideal for rapid prototyping and re-engineering processes. Both languages are supported by a variety of integration and simulation tools from major EDA (electronic design automation) vendors, including Synopsys, Cadence, and Mentor Graphics.

## 2.6 Optimization Techniques for FPGA Implementation

#### 2.6.1: Significance of Ping-Pong Buffers in FPGA Systems

Ping-pong buffers are important in FPGA-based systems due to their unique features and advantages:

**Continuous Data Processing:** Ping-pong provides a mechanism for synchronizing data reads and writes without causing the FPGA system to persist and make the data inconsistent.

**Preventing Data Loss:** By allowing the FPGA to switch between two buffers for data transfer, ping-pong buffers help prevent data loss during high-speed processing, enhancing the system's reliability.

**Optimized Resource Utilization:** These buffers increase the utilization of resources by supporting valuable data in the system, reducing downtime and improving overall performance.

**Reduced Latency:** Ping-pong buffers help reduce data transfer latencies in FPGA systems, instantly improving performance and responsiveness.

**Enhanced Throughput:** The use of ping-pong buffers increases data throughput by managing continuous data, which is important for applications requiring high speed and continuous operation. [12].

2.6.2: Optimization of Performance through Decomposition

**Efficient Resource Utilization:** By dividing the algorithm into stages such as multi-channel data demodulation, FFT, IFFT and matching filtering, the system effectively uses FPGA programs to integrate and enhance the overall system.

**Enhanced Processing Speed**: Breaking algorithms into smaller, manageable tasks can process larger data faster, thus improving the instantaneous performance of the system.

**IP Core Integration**: Basic signal processing such as FFT, IFFT, parallel and DDR controllers use FPGA IP cores to simplify algorithm implementation and improve performance.

This optimization strategy through algorithm decomposition on FPGA-based signal improves the performance of high-frequency active sonar systems.

#### 2.6.3: Efficient Data Handling and Signal Processing in Underwater Using FPGA

In the context of underwater acoustic signal processing, Field Programmable Gate Arrays (FPGAs) play a crucial role from the initial capture of the input signal through to its processing stages. Upon receiving the input signal, the FPGA manages electronic control, orchestrating both data and signal processing within the system. The FPGA first evaluates the incoming data to ensure it meets specific criteria necessary for Fast Fourier Transform (FFT) processing. Once the FPGA verifies that the data satisfies the FFT requirements, it triggers an interrupt signal to the Digital Signal Processor (DSP), indicating that the data is prepared for further processing. This

page-30 of.82

detection mechanism ensures the FPGA operates efficiently, handling the input signal with precision and seamlessly preparing the data for communication with the DSP. By doing so, the system maintains optimal performance and minimizes the risk of errors, ensuring reliable operation in underwater acoustic applications

### 2.7: Future Trends and Research Directions

#### 2.7.1: Enhancing Underwater Security: Challenges and Innovations in Sonar Technology

Now for advanced and more secure surveillance of underwater world, new research trends are seen on the topic. Nowadays underwater security is more vulnerable than ground security, and needs to improve its security level to the extent of adequate measures. Companies and underwater Security bodies are working on to develop high rated and more advanced sonar security systems for unseen underwater threats and risks. [2]

Due to no constant security check ins, unbridled measures, underwater crimes seems to be a easy way to pursue a crime. To make security level more secure as capabilities of ground securities, relevant bodies are keep working to make their underwater security system more advanced and up to date to cater and eliminate any type of crime comes under the vicinity of water. The common crimes observed underwater includes the smuggling of drugs and illegal weapons and substances, and also the disposal of harmful substances that causes serious threats also to the underwater livings.

The project was carried out by a Japanese company in order to improve underwater security and to protect the facilities near the water area, uses the Sonar system having three transducers operating in three different frequencies to cover different area ranges to detect objects and targets nearby and far. They also embedded a high resolution camera on different locations which can detect images and then analyzed by a software in real time, to eliminate the background images and noises. [2]

#### 2.7.2: The Role of Fractional Fourier Transform in Sonar Systems

To make Sonar system more convenient and effective, we do use a Fractional Fourier Transform for major processing operations. It gives more advantages and processing capabilities than a conventional Fast Fourier Transform on Sonar signal processing. When using chirp signals (which frequency increases or decreases with time) for Sonar signal processing, we do use of Fractional Fourier Transform that has the better capability to intercept and process chirp signals rather than Simple Fast Fourier Transform. In the presence of reverberation often Sonar systems make use of chirp signals for processing for better detection. FrFT are also employed in radars to detect moving targets and objects.

#### 2.8: Existing Hardware methods of Sonar Systems

2.8.1: ASIC (Application specific integrated circuit)

In the context of SONAR system hardware solutions, ASICs (Application-Specific Integrated Circuits) provide a highly specialized approach by offering dedicated circuits tailored specifically to the signal processing needs of the system. For SONAR applications, where high-speed, low-latency processing of acoustic signals is critical, ASICs excel by providing optimized performance for tasks such as beamforming, filtering, and target detection. Their architecture is designed to maximize efficiency by focusing exclusively on these tasks, resulting in significantly reduced power consumption and enhanced operational speed, which is crucial for large-scale, continuous operations in commercial or military SONAR systems.

However, due to their fixed-function nature, ASICs lack the flexibility to accommodate future updates or algorithmic changes once manufactured. This limitation makes them less ideal for applications that require frequent upgrades or new features, particularly in evolving fields like SONAR where processing requirements may change over time. The high design and production costs of ASICs also mean they are best suited for long-term deployments where the performance benefits outweigh the need for reconfigurability. In summary, ASICs offer a high-performance, energy-efficient solution for SONAR systems that prioritize stability and efficiency over adaptability.

2.8.2: ASIP (Application Specific Instruction set Processors)

#### Resource Optimize FPGA Implementation of Sonar System

In the context of SONAR system hardware solutions, ASIPs (Application-Specific Instructionset Processors) offer a middle ground between the fixed-function efficiency of ASICs and the programmability of general-purpose processors. ASIPs are equipped with customized instruction

sets that are specifically tailored to the signal processing tasks required by SONAR systems, such as beamforming, FFT, and target detection. This customization enables high performance while maintaining some programmability, which allows for limited adaptability and updates to the system after deployment, such as incorporating new algorithms or enhancing processing functions.

While ASIPs provide more flexibility than ASICs, they are not as adaptable as FPGAs, and their partial programmability can lead to higher power consumption compared to fully optimized ASICs. However, ASIPs are particularly useful in SONAR systems that require a balance between efficiency and adaptability, such as systems that may need occasional updates but do not require the full reconfigurability offered by FPGAs. ASIPs can handle specific SONAR processing tasks efficiently while still allowing for a moderate degree of future adjustments, making them suitable for systems where high performance and some level of flexibility are both necessary.

#### 2.8.3 FPGAs (Field programmable gate arrays)

In SONAR system hardware solutions, FPGAs (Field-Programmable Gate Arrays) offer a highly flexible and reconfigurable platform, making them a preferred choice for complex signal processing tasks. FPGAs enable the implementation of real-time updates and reconfigurations, allowing algorithms such as FFT, IFFT, and beamforming to be optimized and adjusted even

page-34 of.82

#### Resource Optimize FPGA Implementation of Sonar System

after deployment. This adaptability is particularly beneficial in SONAR systems that require continuous evolution, such as those used in research and development, or systems deployed in dynamic environments where algorithmic updates are necessary over time.

One of the standout advantages of FPGAs is their ability to perform parallel processing, which makes them ideal for multi-channel SONAR systems that require high-speed, real-time processing of multiple input channels simultaneously. This capability ensures that FPGAs can efficiently handle the large volumes of data generated by SONAR systems and process them in a timely manner for accurate detection, tracking, and localization.

However, this flexibility comes with trade-offs, including higher power consumption compared to the more specialized ASICs, and the need for greater design effort to develop and optimize the hardware architecture and algorithms. Despite these challenges, the combination of programmability, reconfigurability, and high processing power makes FPGAs an optimal solution for SONAR systems that demand frequent updates, scalability, and efficient real-time signal processing capabilities.

# **CHAPTER 3**

## **METHODOLOGY**

## 3.1 Introduction

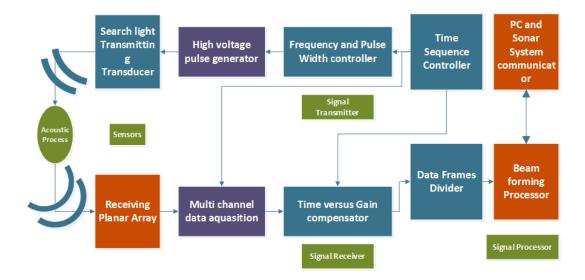

The methodology for this research on "Planar Array Signal Processing and FPGA Applications in SONAR Systems" is designed to leverage the capabilities of FPGA technology for efficient and real-time processing of sonar signals. The project is structured around a six-channel system, where each channel processes data streams with a length of 2048 samples. To ensure the system meets real-time operational requirements, the total processing time is constrained to 19 milliseconds. This methodology focuses on the implementation of advanced signal processing algorithms on FPGA hardware, optimizing the performance of planar array system. The design process involves careful consideration of parallelism, data throughput, and computational efficiency to achieve the desired processing speed and accuracy. The approach also incorporates the integration of signal preprocessing steps, array signal processing techniques, and postprocessing operations, all tailored to the specific requirements of sonar systems.

## 3.2 Conversion process of MATLAB code

### 3.2.1: Implementation of Multi beam Sonar using FPGA

As FPGA is a much better option to run and simulate digital circuits, so we do need to convert MATLAB codes usually into Verilog, to make them appropriate to modeled on Field Programmable Gate Arrays devices. Complex digital circuits and algorithms have an enormous amount of addition and multiplication operations that accelerate the processes needed to execute algorithms. Modern FPGAs have DSP blocks that can process a large number of addition and multiplication operations of conversion of MATLAB codes into Verilog is a little complicated. As MATLAB works in the floating-point format, but FPGA deals with fixed point values. We need to cater to this problem of conversion of floating-point values into fixed numbers so that FPGA configures the results accurately in fixed point. This project mainly has three parts,

- I) The first one is to take FFT of desired bins,

- II) The second is the beamforming process, and

- III) The third and last is to take the IFFT of the previous step results.

Developing a Multi-Beam Sonar System based on Field Programmable Gate Arrays will provide real-time processing and parallel computations of multiplication and addition. We need to optimize our solution as much so that our system uses minimum resources for the implementation. An effective and reliable Sonar System can be implemented by careful consideration of memory requirements and hardware selection.

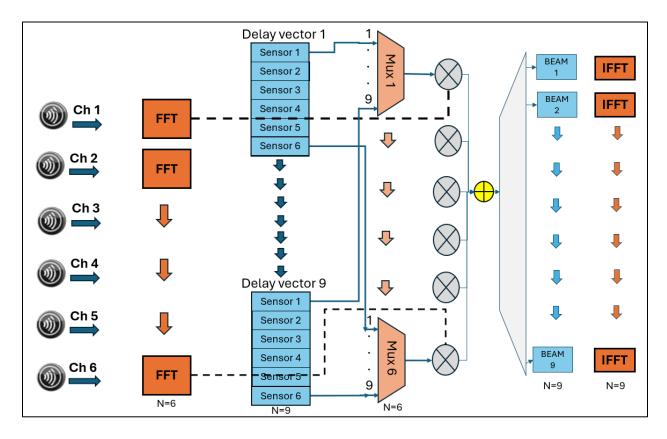

Fig. 3.1 MATLAB Model

## 3.2.2: Matlab to Verilog workflow

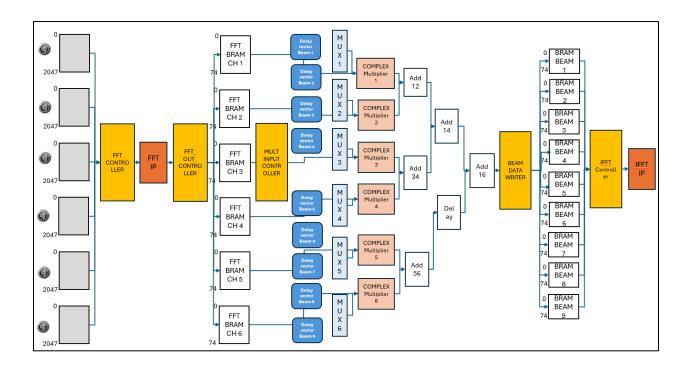

The figure provides an overview of the FPGA architecture designed for the SONAR system, detailing the various blocks integrated into the design. It includes both custom blocks developed in Verilog and IPs such as FFT, IFFT, and beamforming algorithms. Different controllers have been implemented to ensure the smooth and continuous flow of data processing.

In the beamforming section, we utilize delay vectors represented by beamforming coefficients, where each beam corresponds to a specific direction of focus for signal reception or transmission. A total of 9 beams are implemented, with each beam containing 444 coefficients.

These coefficients are stored across 6 ROMs per beam, with each ROM holding 74 coefficients. This results in a delay vector matrix of [9x6x74], where beamforming allows the system to enhance the detection and localization of underwater objects by amplifying signals from target directions and minimizing interference from others.

Multiplexers are used to select the desired beam for multiplication with FFT bins. For example, selecting beam 1 is done by setting the multiplexer control line to '0001,' wiring the beam for the multiplication process. Demultiplexers are employed to route the results from each beam to its corresponding storage location, with 9 RAMs dedicated to storing the results for each beam. This structured approach allows for precise control over beam selection and data flow in the system.

The given MATLAB code consists of 4 codes, in which the step-by-step process of the Sonar system has been accumulated. As discussed earlier there are three main steps in the whole process. Taking The Fast Fourier Transform of the signal, then operation of beamforming is done, and last, signals are converted back into their originated form. Our Sonar system consists of 6 sensors, which means, data is coming from six different sensors forming a single row or column. Usually writing MATLAB code for digital operations or for complex algorithms takes less time as MATLAB provides just simple commands for complex algorithms like for Fast Fourier Transform "FFT" command is used for incoming signals. The input signal is composed of 16 bits. The input length of each signal consists of 2048 samples.

## 3.2.3: FFT processing using Xilinx IP and Verilog for efficient utilization

In FPGA, FFT algorithm takes complex input in which the most significant half bits are imaginary and the least significant half bits are real parts. So, we consider an input as both a real and imaginary part. Also input to the FFT is of 32 bits, 16 for real, and 16 for imaginary. As MATLAB values are in floating point, so first, the input values we have for signals of 2048 samples will converted to fixed point number, to make them capable of going into the process of FFT. In Verilog, we don't have a simple command for FFT, but we do have a Xilinx IP for FFT in Vivado. The IP is customizable, we can use it to take FFT of 1024 length, 2048 length or length bigger than it or lesser than it. We have also an option to change the bit width of input signals. The Xilinx FFT IP of Vivado consists of many signals evaluating different phases capturing in our input signals. It works like a Master and Slave interface. It acts like a Slave when taking input, while signals act like a Master at that stage. Like While at the output, the core acts like a Master and we are receiving the operated form of signals, so we act like a Slave. We can use more than one FFT IP in our project, but to keep it resource-efficient, we reuse the FFT core, which takes very less resources.

We store our actual inputs of six signals into the Block RAMs. Inputs are kept inside RAMs in the. Coe format. So, we have 6 block Rams before FFT IP in our design to store inputs. Now as our signal original form is analogous, so we need to change it in binary format to make it eligible for the FPGA process. We do take the help of ADC modules in starting of our project design. We have use Verilog language syntax in our design, where needed. So, each input passes through ADC modules first, then they stored in their block Rams. Each input starts their way as with each positive edge of clock. So, we do need to keep them in different states before reaching into a single FFT core. We make six controllers, one to each block Ram. Counters in each controller summed their

page-40 of.82

rotation to a bigger value as we move from top to bottom in block Ram controllers. First signal input goes straight into FFT core, without goes into any wait state.

All the remaining inputs are under wait at that time. At the time we get the output from FFT of first signal, wait for the second signal input will get over. Now the second signal goes into the FFT core for the processing, and the remaining signal counters are still under the wait condition. Again after, we get the FFT results for the second input, the third input start to go into the FFT core and like this way, the whole process will go on till the last FFT output of channel 6 comes out from the core. To control these controllers, we do use another controller named "big controller" that smooth the process of signal processing.

## 3.3: Selective FFT bin extraction and beamforming using Verilog

As per the requirement of the project, we don't need the whole FFT results of signals for further processing. From 2048 output FFT length we just need to take out bins ranging from 697-769. So, we make another controller named "bins controller" to do the task of filtering out the desired bins. These bins we are required for beamforming process. So, what we do basically here in beamforming, is to multiply the desired bins of FFT result with the coefficients values we have stored in (ROMS). So, to do the whole process of taking FFT of six different channels by utilizing a single FFT core is much complicated than taking the FFT in MATLAB. It just requires a single command to do the task. Otherwise for filtering bins just require a four-line code to do it, in MATLAB. For beamforming process in MATLAB requires just some commands too for a multiplication process. Now in Verilog it requires a little work to do. Firstly, we store the desired

bins into separate six memories.

### 3.3.1: Sequential Beamforming with selective FFT bins using Verilog

Bins controller doing the work of bridge for signals from FFT IP core to these memories, where bins will get stored. As per the description of the project there are nine angles from which the data is coming. Practically, we use the term beams for angles. These desired bins will have to be multiplied with each one of beams. So, each beam should consist of six ROMS holding the coefficients, so that it multiplied with its corresponding RAMS of desired bins. We have total of 9 beams, and each beam comprised of 6 ROMS holding the coefficients. In that way bins will be multiplied with each beam one by one. To keep the design resource efficient, we used six complex multipliers for whole multiplication. Angle 1 coefficients first multiplied with desired bins memories, with the help of complex multipliers, then angle 2 coefficients will get under way for the multiplication with desired bins memories. So, angle coefficients multiplied serially, one after one. This way, it takes little time, but we can save much resources, which we can't with parallel computations. To control the multiplication process, we designed one more controller named "multiply-controller", and 6 Multiplexers, for alternately and timely selection for multiplications. Multiply controller vary from 9 different states, in each stage the desired coefficients of a beam get multiplied with the desired bins.

# **CHAPTER 4**

# **IMPLEMENTATION DETAILS**

## 4.1: Introduction

The implementation phase of the thesis focuses on translating the theoretical concepts and design methodologies discussed in the preceding chapters into a practical, functional system. This chapter details the step-by-step process of implementing a planar array signal processing system within a SONAR application, using Field Programmable Gate Arrays (FPGAs) as the primary platform. Given the inherent complexity and high computational demands of SONAR systems, particularly in real-time signal processing scenarios, FPGAs present a compelling solution. They offer parallel processing capabilities and the flexibility to customize digital circuits for specific tasks, making them an ideal choice for handling the rigorous requirements of multi-beam SONAR systems.

Fig. 4.1 Verilog Code Block diagram.

# 4.2: System Implementation

The architecture of multi-beam sonar implemented on FPGA may vary depending on the specific project requirements. In this project linear array multi-beam sonar is implemented, in which data is coming from six different channels.

# 4.2.1: Software Configuration

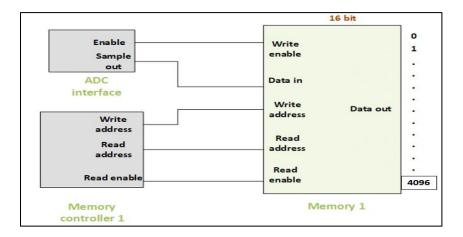

For each channel, the input data first passes through an Analog digital converter, which converts that signal to a 16-bit digital signal and the length of each signal is 2048 samples. After passing through ADC these 2048 samples are stored in the memories (Block RAM) placed after each channel.

For controlling the writing and reading of data from and into memories we make memory controllers to control the flow of data.

Fig. 4.2 Data Flow

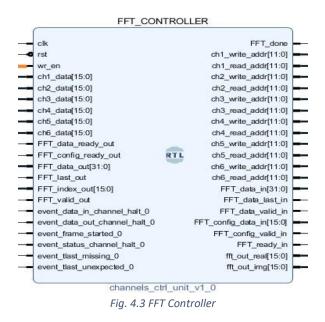

To the continuous flow of data, the length of the memories should be double corresponding to the input sample length which is 4096. While focusing on the first target of the project, we take the FFTs of six channels by utilizing a single FFT IP from Xilinx. To control the input data while taking FFT, there is a controller named the FFT controller. This controller is responsible for the flow of data before reaching the FFT IP. All the memories are filled at the same time with 2048 samples, after this state machine takes the controller to the read state. Memories data out will go directly into their corresponding inputs of the FFT controller. As all the memories have their corresponding data out at the same time, the controller is designed to take the inputs one by one from the memories and go to the FFT IP. There are individual valid for all the outputs of the memories so that the data will come when their corresponding valid becomes high. At the output

of the FFT controller, serial data is coming out that goes directly to the input of the FFT IP. FFT IP takes data serially.

As our computation time is 19 milliseconds, the memory size should be 4096 locations. To establish the continuous flow of data, data will be out from memories after it is half-filled. The data in memory 1 will go to the read mode when the write addresses reach to 2048 location. It will continue to write data into memory and when the write addresses reach to 4096 location it will again start streaming out data to FFT IP. Each memory is of 16 widths as our input data is of 16 bits and 4096 locations are there in every memory.

## 4.2.2: FFT Integration

Xilinx provides a variety of IPs (intellectual properties). IPs make work much easier for the users and for the digital designers. They are easier to use as coding requires much time to analyze the design. For fast Fourier transform we set the s\_axis\_config\_tvalid to '1'. Calculating the FFT of different channels requires careful consideration. Setting an appropriate scaling range is the important factor for efficient FFT results of six inputs. S\_axis\_config\_tdata is used to set the range of scaling factors and the choice to take the FFT or IFFT. There are also different events available here in the IP. Events are used to test different scenarios of the data.

The data of channels goes serially into the FFT core, so the memory controllers undergo wait conditions till the transfer of the first channel data and so on. The second channel input enters in FFT core, after we receive the output of the first input. To operational the FFT IP core there are a few settings inside the IP core that you need to address before using it in the project. According to the project requirements, we change the setting of the IP core.

| Fast Fourier Transform (9.1)                                                                      |                                                      |     |

|---------------------------------------------------------------------------------------------------|------------------------------------------------------|-----|

| Occumentation IP Location                                                                         |                                                      |     |

| IP Symbol Implementation De 4 ▶ Ξ                                                                 | Component Name xft_0                                 |     |

| Show disabled ports                                                                               | Configuration Implementation Detailed Implementation |     |

|                                                                                                   | Number of Channels 1                                 |     |

|                                                                                                   | Transform Length 2048 V                              |     |

|                                                                                                   | Architecture Configuration                           |     |

| M_AXIS_STATUS + H<br>M_AXIS_DATA + H<br>H S_AXIS_DATA event (rame yarted -                        | Target Clock Frequency (MHz) 100 🚳 [1 - 1000]        |     |

| + S_AXIS_CONFIG event_tast_unexpected -<br>acts event_tast_missing -                              | Target Data Throughput (MSPS) 50 💿 [1 - 1000]        |     |

| - action event_fl_oveniov -<br>e arcistn event_status_channel_hak -<br>event_status_channel_hak - | Architecture Choice                                  |     |

| even_data_out_channel_hak                                                                         | Automatically Select                                 |     |

|                                                                                                   | Pipelined, Streaming I/O                             |     |

|                                                                                                   | Radix-4, Burst I/O                                   |     |

|                                                                                                   | Radix-2, Burst I/O                                   |     |

|                                                                                                   | Radix-2 Lite, Burst I/O                              | « S |

Fig. 4.5 FFT IP Core Settings

The clock frequency is 100 MHz, transform length is 2048 FFT point. Pipelined streaming, I/O is fast but utilizes more hardware resources as compared to Burst I/O which reuses the butterfly but saves resources.

| P Symbol Implementation De (↓ ▶ =                                                                                                                   |                                                      |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--|

|                                                                                                                                                     | Component Name xfft_0                                |  |

| Show disabled ports                                                                                                                                 | Configuration Implementation Detailed Implementation |  |

|                                                                                                                                                     | Data Format Fixed Point ~                            |  |

|                                                                                                                                                     | Scaling Options Scaled ~                             |  |

|                                                                                                                                                     | Rounding Modes Truncation ~                          |  |

| M_AXIS_STATUS +                                                                                                                                     | Precision Options                                    |  |

| # + S_AXIS_DATA         event_frame_started           # + S_AXIS_CONFK3         event_itast_unexpected           = acit         event_itast_missing | Input Data Width 16 V Phase Factor Width 16 V        |  |