## Design and Implementation of RISC-V Processor with ML Accelerator

By

Faizan Ahmad Enrollment No. 01-133192-030

Sawera Aslam Enrollment No. 01-133192-123

Hamna Shakil Enrollment No. 01-133192-037

## Supervised By

Dr. Atif Raza Jafri

Session 2019-23

This Report is submitted to the Department of Electrical Engineering, Bahria University, Islamabad. In partial fulfillment of requirement for the degree of BS(EE).

## Certificate

We accept the work contained in this report as a confirmation to the required standard for the partial fulfillment of the degree of BS(EE).

Head of Department

Supervisor

Internal Examiner

External Examiner

### Dedication

We express our gratitude to our family, friends, and mentors who have been a constant source of support and encouragement throughout our dissertation journey. Our parents, in particular, have played a significant role in motivating us to persevere through challenges. We extend our heartfelt thanks to our supervisors for their guidance and assistance in developing our skills, which will undoubtedly prove valuable in our future endeavors. This dissertation is dedicated to all those who have helped us along the way.

### Acknowledgments

We would like to express our gratitude to our Creator Allah S.W.T. who primarly helped in each and every step of achieving any progress in this project. We can say with full and complete confidence that without His blessings and help we would never be able to accomplish such a huge project and InshaAllah He will always be there for us. Secondly He gave us such good and helping friends and supervisors who also guided us whereever we were stuck. Thank you Dr. Atif Raza Jafri and Mr. Muhammad Ali for being supportive and an encouragement for us in this project.

#### Abstract

We are currently witnessing the dawn of a new industrial revolution, characterized by the rapidly changing industrial landscape. In this revolution, RISC-V has emerged as a widely used term to describe the development of custom processors designed to meet the power and performance requirements of newer workloads for AI, ML, and IoT. RISC-V is an open standard ISA that is built on RISC principles and plays a critical role in linking software and hardware layers of computer abstraction. The primary drivers of this product include building custom processors, boosting speed, reducing costs, enhancing security, developing a platform for new students in this field, promoting innovation and skills, and competing with other companies such as Intel (x86), ARM (ARM ISA), and others.

This project presents the implementation of a RISC-V processor on FPGA with an integrated accelerator for machine learning (ML) applications. The processor used in this project is VexRiscv with ztachip accelerator. The main objective of this project is to develop a hardware system with high performance and efficiency for ML applications. To achieve this objective, the VexRiscv processor is modified to transfer tensor instructions to ztachip for accelerating ML computations.

The implementation of this integrated system is carried out on an FPGA platform, which allows for flexibility and easy reconfiguration. The design is verified using debugging tools and is tested on various ML applications. The results show that the designed processor with the integrated accelerator outperforms traditional processors and accelerators in terms of both speed and energy efficiency. The tensor instructions of ztachip for ML computations also provide significant speedup compared to standard RISC-V instructions.

Overall, the project demonstrates the feasibility and effectiveness of implementing a RISC-V processor with an integrated accelerator for ML applications. This work has implications for the development of highperformance and energy-efficient RISC-V accelerators for various applications, particularly in the field of ML.

# Contents

| 1        | Inti | roduction                                            | 1  |

|----------|------|------------------------------------------------------|----|

|          | 1.1  | Project Background                                   | 3  |

|          | 1.2  | Project Overview                                     | 4  |

|          |      | 1.2.1 Keypoints about RISC-V                         | 4  |

|          | 1.3  | Problem Statements                                   | 8  |

|          | 1.4  | Project Objectives                                   | 12 |

|          | 1.5  | Project Scope                                        | 14 |

|          |      | 1.5.1 RISC-V                                         | 14 |

|          |      | 1.5.2 Machine Learning                               | 20 |

| <b>2</b> | Lite | erature Review                                       | 22 |

|          | 2.1  | Introduction                                         | 23 |

|          | 2.2  | Purpose of the Review                                | 24 |

|          | 2.3  | RISC-V based Pakistan's first processor              | 24 |

|          | 2.4  | UC Berkeley made RISC-V Chips                        | 26 |

|          | 2.5  | Power Management Integrated RISC-V Processor SoC Op- |    |

|          |      | erating at Submicrosecond Timescales                 | 27 |

|          | 2.6  | RISC-V Processor Designed for Space Systems          | 28 |

|          | 2.7  | RISC-V and PULP                                      | 28 |

|          |      | 2.7.1 Ibex Core                                      | 29 |

|          |      | 2.7.2 Zeroriscy Core                                 | 31 |

|          | 2.8  | RISC-V Accelerator for Post-Quantum Cryptography     | 39 |

|          | 2.9  | RISC-V Accelerator designed for Ascon                | 40 |

| 3        | RIS  | SC-V Processor                                       | 42 |

|          | 3.1   | $Introduction \ldots \ldots$ | 43 |

|----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

|          | 3.2   | VexRiscv                                                                                                                                            | 44 |

|          |       | 3.2.1 Performance Score Comparison                                                                                                                  | 45 |

| <b>4</b> | RIS   | SC-V Accelerator for ML Applications                                                                                                                | 47 |

|          | 4.1   | Introduction                                                                                                                                        | 48 |

|          | 4.2   | Ztachip as DSA                                                                                                                                      | 49 |

|          |       | 4.2.1 Limitations                                                                                                                                   | 50 |

|          | 4.3   | Ztachip Software Stacks                                                                                                                             | 51 |

|          | 4.4   | Hardware Architecture                                                                                                                               | 52 |

| <b>5</b> | Inte  | egration of RISC-V Processor with ML Accelerator                                                                                                    |    |

|          | on    | FPGA                                                                                                                                                | 60 |

|          | 5.1   | Introduction                                                                                                                                        | 61 |

|          | 5.2   | Advantages of using FPGA for<br>Implementation                                                                                                      | 61 |

|          |       | 5.2.1 Genesys 2                                                                                                                                     | 62 |

|          | 5.3   | Steps of Integration                                                                                                                                | 65 |

|          | 5.4   | Integrated Design Architecture                                                                                                                      | 66 |

|          | 5.5   | Process Flow                                                                                                                                        | 75 |

|          | 5.6   | Hardware Setup                                                                                                                                      | 75 |

| 6        | Cor   | nclusion                                                                                                                                            | 78 |

|          | 6.1   | Summary and Implications                                                                                                                            | 79 |

|          | 6.2   | Abilities                                                                                                                                           | 80 |

|          | 6.3   | Result                                                                                                                                              | 81 |

|          | 6.4   | Performance                                                                                                                                         | 85 |

| R        | efere | nces                                                                                                                                                | 87 |

# List of Figures

| 1.1  | Layers of Abstraction of Computer Architecture                | 2  |

|------|---------------------------------------------------------------|----|

| 1.2  | RISC-V Logo                                                   | 4  |

| 1.3  | Descrption of RISC-V ISA                                      | 5  |

| 1.4  | Open Source RISC-V ISA [?]                                    | 6  |

| 1.5  | Open-Source vs. Closed                                        | 7  |

| 1.6  | Pakistan Imports of Electrical, and Electronic Equipment -    |    |

|      | 2022                                                          | 8  |

| 1.7  | Electronic Devices based on Microprocessor                    | 10 |

| 1.8  | 50 Years of Technology Scaling                                | 11 |

| 1.9  | NASA selects RISC-V for Space Exploration                     | 15 |

| 1.10 | Description of four Distinct Processor Families of SiFive     |    |

|      | Core IP Portfolio based on the RISC-V ISA $\hdots$            | 16 |

| 1.11 | Specification of Alibaba Roma RISC-V Laptop $\ . \ . \ . \ .$ | 17 |

| 1.12 | Google selected SiFive                                        | 18 |

| 1.13 | China showing interest in RISC-V                              | 19 |

| 1.14 | Machine Learning, Its Importance, Types, and Applications     | 20 |

| 2.1  | NUST developed Pakistan's First Processor based on RISC-V     | 24 |

| 2.2  | Ibex Core Block Diagram                                       | 29 |

| 2.3  | The Distribution of Power among the Three Core Units          |    |

|      | while Running Coremark at a Frequency of 100MHz and           |    |

|      | a Voltage of $1.2V$                                           | 32 |

| 2.4  | The Total Area Occupied by all the Core Units in KGE          |    |

|      | (thousands of square millimeters)                             | 33 |

| 2.5  | Block Diagram of zeroriscy Core                               | 34 |

| 4.1 | Methodology                                | 52 |

|-----|--------------------------------------------|----|

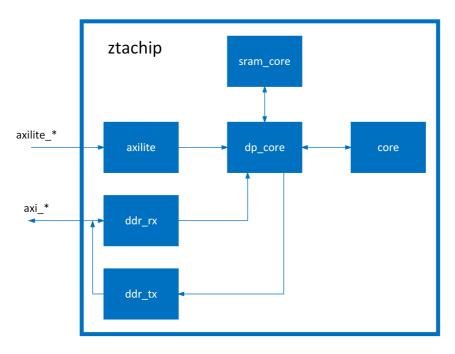

| 4.2 | ztachip Hardware Architecture              | 54 |

| 5.1 | Genesys 2 FPGA Board                       | 64 |

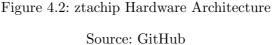

| 5.2 | Integrated System Block Diagram            | 67 |

| 5.3 | Hardware System                            | 76 |

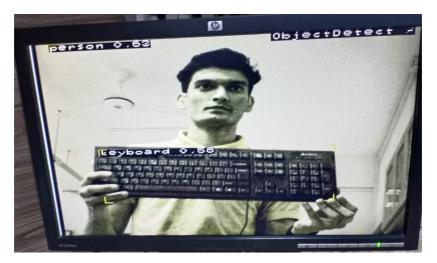

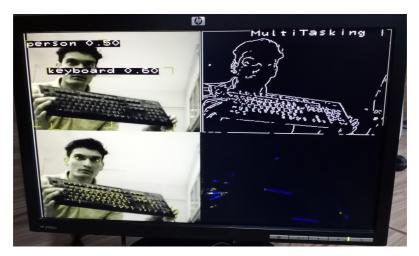

| 6.1 | Object Detection of Person and Keyboard    | 81 |

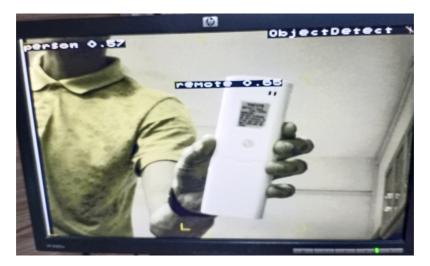

| 6.2 | Object Detection of A.C. Remote            | 82 |

| 6.3 | Object Detection of Umbrella               | 82 |

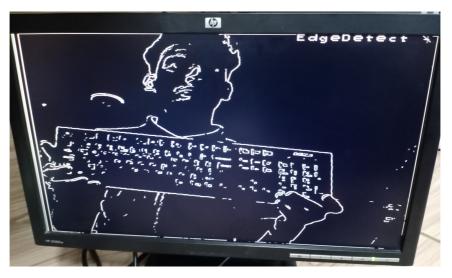

| 6.4 | Edge Detection of Person and Keyboard      | 83 |

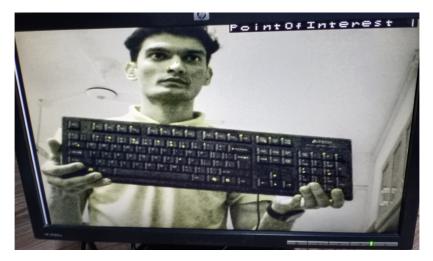

| 6.5 | Point of Interest on Person and Keyboard   | 83 |

| 6.6 | Motion Detection on Keyboard               | 84 |

| 6.7 | All Four ML Algorithms running in Parallel | 84 |

# List of Tables

| 2.1 | Specifications of NTiny-E                          | 25 |

|-----|----------------------------------------------------|----|

| 2.2 | Comparison of Different PULP Cores                 | 31 |

| 2.3 | Instruction Fetch Signals                          | 36 |

| 2.4 | LSU Signals                                        | 38 |

| 3.1 | Benchmark Score Comparison of Different Processors | 46 |

| 4.1 | VLIW Instruction Format                            | 57 |

| 6.1 | Benchmark Score Comparison of ztachip with Nvidia  | 86 |

## Abbreviations

- A Atomic Instructions

- ADC Analog to Digital Converter

- AEAD Authenticated Encryption with Associated Data

- AI Artificial Intelligence

- ALU Arithemetic and Logic Unit

- AMD Advanced Micro Devices

- APB Advanced Peripheral Bus

- ARM Advanced RISC Machines

- ASIC Application Specific Integrated Circuit

- ATSC Advanced Television Systems Committee

AXI Advanced eXtensible Interface

B Bit Manipulation

BOOM Berkeley Out of Order Machine

- C Compressed Instructions

- CEO Chief Executive Officer

- CHIPS Common Hardware for Interfaces, Processors and Systems

- CISC Complex Instruction Set Architecture

- CLB Configurable Logic Block

- CMOS Complementary Metal Oxide Semiconductor

- CPU Central Processing Unit

- CSR Control and Status Register

- DC Direct Current

- DDR Dual Data Rate

- DFA Differential Fault Attacks

- DLX Deluxe

- DMA Direct Memory Access

- DMIPS Dhrystone Million Instructions per Second

- DMR Dual Modular Redundancy

- DPA Differential Power Attacks

- DSA Domain Specific Architecture

- DSL Domain Specific Language

- DVD Digital Video Disc

- E Embedded

- ECC Error Correcting Codes

- EECS Electrical Engineering and Computer Science

- EEES Energy Efficient Embedded Systems

- ETH Eidgenössische Technische Hochschule

- EX Execution

- F Single-Precision Floating Point

- FIFO First In First Out

- FMA Fused Multiplication and Addition

- FMS Fused Multiplication and Subtraction

- FPGA Field Programmable Gate Arrays

- FPS Frames Per Second

- G General

- GCC GNU Compiler Collection

- GDB GNU Debugger

- GFLOPS Giga Floating-Point Operations per Second

- GHz Giga Hertz

- GOPS Giga Operations Per Second

- GPIO General Purpose Input Output

- GPR General Purpose Register

- GPU Graphic Processing Unit

- GUI Graphical User Interface

- HDL Hardware Description Language

- HDMI High Definition Multilmedia Interface

- HPC High Performance Computing

- HPSC High Performance Spaceflight Computer

- HS Horizontal Sync

- I Integer Base ISA

- IBM International Business Machines

- ID Instruction Decode

- IEEE Institute of Electrical and Electronics Engineers

- IF Instruction Fetch

- IIS Integrated Systems Laboratory

- INT Integer

- IoT Internet of Things

- IP Intellectual Property

- ISA Instruction Set Architecture

- JTAG Joint Test Action Group

KB Kilo Byte

kGE Kilo Gate Equivalent

LSU Load and Store Unit

M Multiplication and Division

MAC Multiplication and Accumulation

Mbps Mega Bits Per Second

MHz Mega Hertz

MIG Memory Interface Generator

mm Milli Meter

#### mW Milli Watt

MXU Matrix Multiplication Units

NASA National Aeronautics and Space Administration

NESCOM National Engineering and Scientific Commission

NUST National University of Science and Technology

OCD On Chip Debugger

OTP One Time Programmable

OV Omni Vision

PC Personal Computer

PGC Programmable Gain Control

- PQC Post Quantum Cryptography

- PULP Parallel Ultra Low Power

- PWDN Power Down

- PWM Pulse Width Modulation

- QSPI Quad Serial Peripheral Interface

- RGB Red Green Blue

- RISC Reduced Instruction Set Architecture

- **RISC-V** Reduced Instruction Set Computer Five

- RTL Register Transfer Level

- RV RISC-V

- SA Systolic Arrays

- SDRAM Synchronous Dynamic Random Access Memory

- SFA Statistical Fault Attacks

- SHL Shift Left

- SHR Shift Right

- SIFA Statistical Ineffective Fault Attacks

- SoC System on Chip

- SOI Silicon On Insulator

- SPI Serial Peripheral Interface

- SRAM Static Random Access Memory

SSD Single Shot Detection

symbol description

TPU Tensor Processing Units

UART Universal Asynchronous Receiver Transmitter

UC University of California

US United States

USB Universal Serial Bus

V Volts

VCR Videocassette Recorder

VDMA Video Direct Memory Access

VGA Video Graphics Array

VHDL VHSIC Hardware Description Language

VLIW Very Long Instruction Word

VS Vertical Sync

W Watt

YAML Yet Another Markup Language / YAML Ain't Markup Language

# Chapter 1

# Introduction

Design and Implementation of RISC-V Processor with ML Accelerator 1

Our project is "Implementation of RISC-V based processor on FPGA kit with integrated accelerator for ML algorithms". It is the initial and significant step towards innovation and improvement. Software and hardware interface is the important abstraction layer in the computer system. RISC-V is distinctive, innovative, because it is a common, free, open-source ISA to which software can be interfaced, hardware can be design, and processors can be built to support it.

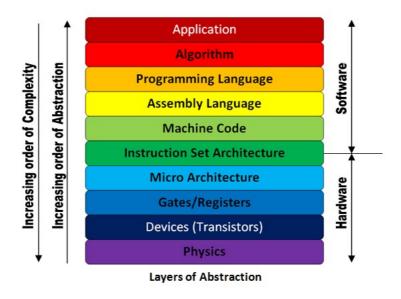

Figure 1.1: Layers of Abstraction of Computer Architecture Source: Secplicity

As this figure shows different layers in an architecture of computer in order. The most important of them all is the middle most layer named as Instruction Set Architecture. It links the software and the hardware of any computer or processor based system i.e. laptops, cellphones, electronic devices etc.

### 1.1 Project Background

RISC-V, which is based on RISC architecture and pronounced as "riskfive," was created at the University of California, Berkeley. The concept of simpler and more effective computers had been around since the 1980s, but the design principles were not yet fully understood. There was academic interest in computers with high power and the ability to execute multiple instructions per cycle. DLX, a RISC processor architecture, was designed by John L. Hennessy and David A. Patterson with a focus on education and research. Later, David Patterson contributed to the development of RISC-V. Although researchers created DLX using field programmable gate arrays, it was not intended for commercial use.

The earlier versions of ARM CPUs that utilized RISC architecture had an instruction set that was available in the public domain and is still supported by the GNU Compiler Collection (GCC), a widely used free software. GCC can compile code, manage library dependencies, and convert high-level programming languages such as C/C++ into assembly code, which can then be transformed into executable files. While there were three open-source core designs based on this instruction set, they were never actually manufactured. OpenRISC is an open-source instruction set architecture (ISA) that is based on DLX and can be supported by GCC and Linux implementations, although there have been very few commercial implementations to date. Krste Asanovic, along with some of his graduate students, embarked on a brief three-month project in 2010 with the goal of creating a design that would appeal to both academic and industrial users. David Patterson, the creator of Berkeley RISC, also joined the project, which became known as RISC-V and was the fifth generation of his RISCbased research projects. Despite its initial brief timeline, the project had

Figure 1.2: RISC-V Logo Source: RISC-V Foundation

significant impact and was successful in achieving its objectives.

## 1.2 Project Overview

This chart shows some of the description of RISC-V ISA. It comes with three variants i.e. 32, 64 and 128 bits. It has various optional extensions e.g. M extension contains instructions related to multiplication and division, F extension means that it will support single precision floating points of different width depending on the variant being used and many other extensions. It also contains 16 or 32 general purpose registers again depending on the extension being used either I (32) or E (16). It supports little endian while reading or writing in memory.

#### 1.2.1 Keypoints about RISC-V

- The RISC-V instruction set architecture is a free and open ISA that draws on three decades of RISC architecture development. It is designed to be simple and easy to understand, with a reduced instruction set suitable for both lower-power embedded systems and high-performance computers. RISC-V's open nature and simplified instruction set make it accessible for anyone to use freely and contribute their skills and work towards its development.

- RISC-V has flexible nature, which means that it can be used for

Figure 1.3: Descrption of RISC-V ISA Source: Wikipedia, The Free Encyclopedia

embedded applications as well as for high end computations. This is possible due to its feature of allowing optional extensions. It's base extension, although, has all the instructions required to compile a C program but there are also optional extensions e.g., for multiplication or atomic operations or vector operations etc. If RISC-V is being used by an individual or a small-scale industry which require it to perform low end computations or want to use less hardware, then they can use the base extensions or any other optional extension along with it. But

Figure 1.4: Open Source RISC-V ISA [?] Source: Microcontroller Tips

if RISC-V is being used by a very large organization and applications required are high end and need to perform a lot of computations or being used in a PC or laptop then RISC-V can have all other required extensions to perform those complex operations in no time. No wonder NASA and Google are also start using RISC-V in their space missions and data centers respectively.

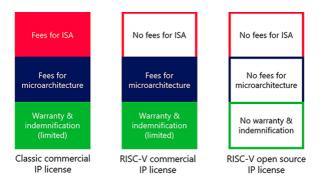

• RISC-V ISA is more secure and reliable as compared to other ISA's because when we will build our own processors using RISC-V ISA we will surely be knowledgeable about the algorithms and logic inside of that processor so there will be probably zero possibility of data thieving. If we talk about other processor providers or ISAs, then Intel and ARM are on the top of the list. Intel, as we all know, doesn't allow access to its ISA i.e., 8086 or x86 etc. Whereas ARM has its ISA named as ARMISA and a lot of companies make processors for cellphones based on ARMISA e.g., Qualcomm or Snapdragon etc. But ARM doesn't allow the access to its ISA for free. It gives license to their customers, and which can be pretty out of range for

small scale companies. It erects a barrier to the commercialization of successful research ideas.

• RISC-V uses simple instructions in its instruction set as compared to other ISAs which uses complex instructions both in form of no. of operations as well as size of the instructions which is not same for all instructions. Intel ISA x86 was traditionally built as a CISC (Complex Instruction Set Computer) ISA, while ARM was built as RISC (Reduced Instruction Set Computer). Originally, CISC machine's goals to execute fewer, more complex instructions and do more computation in single instruction. RISC based on simpler instructions that are easier and faster to execute and only execute one instruction per cycle.

Figure 1.5: Open-Source vs. Closed Source: Bluespec

• RISC-V will support both proprietary and open implementations. Another aspect of RISC-V which makes it different from other ISAs is that it allows, and in fact, encourage custom extension. Adding custom extensions is a feature which can bring innovation to the the computer industry. It means that anyone can add any self-made instruction into the ISA of RISC-V for their own use as well as others which will be useful for any specific work load. This is a new way of getting things faster.

### **1.3** Problem Statements

• Pakistan doesn't make its own processors whenever we require a processor, we import it from foreign countries.

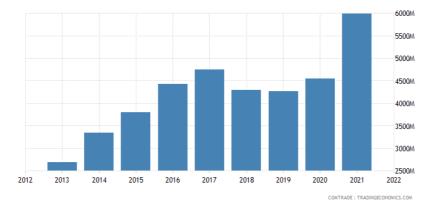

Figure 1.6: Pakistan Imports of Electrical, and Electronic Equipment - 2022

#### Source: Trading Economics

As we can see in this bar graph the import of Pakistan of electronic products is increasing every year. Most of these products have a processor in their core doing all the working and computations. So the lack of processor is one of the major issues due to which we are unable to develop our own electronic products.

• Now to make any processor one should have access to any ISA. But unfortunately, we don't have access to the ISAs of other processors (for free) like Intel's ISA x86, ARM's ISA ARMISA and many others. So, there is a need to explore and implement an ISA to develop our own processor or to develop our own ISA but it is not a simple task to do.

- Another major issue of using imported foriegn country made processors is of security. We don't know what kind of algorithms are used inside those processors and there is a chance of data stealing or hacking. Such issues are very critical especially in those areas where we need tight securities for example in military areas, NESCOM etc. Any individual would also not like that his or her personal data may be accessed by any unknown person so this issue is also crucial in cloud computing, business purposes, import and export, personal information and so on.

- In the field of processor designing, Pakistan lags behind due to the lack of a suitable platform for engineers in this domain. This is unfortunate, as processors are a crucial component in both computer and electronics industries. Most daily-use products such as home appliances, cars, planes, medical devices, and security systems incorporate microprocessors in some way.

Despite this, it is rare for electrical or electronics engineers to have knowledge about processor designing. The importance of microprocessors is evident in the wide range of products that rely on them, from televisions, VCRs, and DVD players to elevators, computer servers, and even some doors with automatic entry. Raising awareness about processor design can help bridge the gap and enable Pakistan to keep up with global advancements in this domain.

• Moore's law, proposed by Gordon Moore in 1965, predicted that the number of transistors on semiconductor chips would double approximately every 18 months. This implied that computing capabilities

Figure 1.7: Electronic Devices based on Microprocessor Source: VectorStock

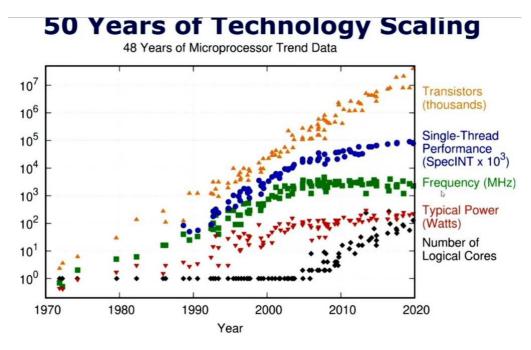

would become significantly faster, smaller, and more efficient over time. However, chip densities are no longer doubling every 18 months. As we can see in this graph that although transistor size are almost going ideal but the clock frequency has kind of stopped at almost 5 GHz. Clock frequency is one of the major factors on which computational speed of a processor depends. Now to overcome this issue more number of cores are being implemented in a single processor but the issue in this method is one that number of cores per chip cannot exceed after a certain limit and the other is that it consumes more power. Power consumption is also a big hurdle in going advance in computer technology. So there is a need of an energy efficient and powerful processor or computer system (RISC based).

• Machine Learning is widely used nowadays to achieve artificial in-

Figure 1.8: 50 Years of Technology Scaling Source: Data Center Knowledge

telligence. There are a lot of applications of AI nowadays such as image recognition, object detection, image classification, in medical and military fields and a lot more. Normally PCs are use to achieve desire output. And nowadays CPUs and GPUs (Graphic Processing Units) are used in PCs. If we use CPU to do the required computations, then it takes a lot of time which most users don't like. On the other hand, GPUs are not affordable by small scale industries or individuals working on a project. Other than that, for space constraint applications like security camera in a military or sensitive area. The system for the computations needs to be placed near the security camera to detect the presence of any intruder. These applications require embedded platforms to do the computations in less time and using less space. So there is also a need for domain specific accelerator to run the ML algorithms faster than CPU and costs less than GPU.

### 1.4 **Project Objectives**

- 1. First objective is design and implementation of RV32IMC processor on FPGA. The HDL (hardware description language) used for this purpose is SpinalHDL. SpinalHDL is a language to describe digital hardware. It is used to generated VHDL/Verilog files. It is much more powerful than VHDL, Verilog, and SystemVerilog in its syntax and features Much less verbose than VHDL, Verilog, and SystemVerilog. It allows you to use Object-Oriented Programming and Functional Programming to elaborate your hardware and verify it. In this RISC-V processor description, RV32I is base instruction set, M extension is for multiplication and division instructions and C is for compressed instructions. Compressed instructions actually mean that instead of 32 bit of instruction size, most commonly used instructions will be of 16 bit width so that they occupy less instruction memory. RISC-V has many optional extensions but we are using only two extensions which are enough for our general-purpose processor design. We will test the processor by making software application in C language, then we can clearly see the result if our processor will show the results for exact same implementations which we will give in C language. The core we are using is named as VexRiscv and was developed by same developer as of SpinalHDL and is available on GitHub [1].

- 2. The second objective of the project is to implement a specialized machine learning accelerator for different ML applications, which will

increase the computational speed of those algorithms and provide faster results. The accelerator will take on ML related tasks from the processor and expedite the process, delivering results back to the processor with minimal delay. One example of a RISC-V accelerator designed for vision and AI edge applications is ztachip, which can operate on low-end FPGA devices or custom ASICs, making it a highly efficient and low-power solution for embedded systems. Compared to a non-accelerated RISC-V implementation, ztachip can provide acceleration capabilities of up to 20-50x for many vision and AI tasks. It even surpasses the performance of a RISC-V processor that has a vector extension. One of ztachip's standout features is its innovative tensor processor hardware, which enables it to accelerate a wide range of different tasks, including edge detection, optical flow, motion detection, color conversion, and the execution of TensorFlow AI models. This sets it apart from other accelerators that are limited to accelerating a narrow range of applications, such as convolutional neural networks.

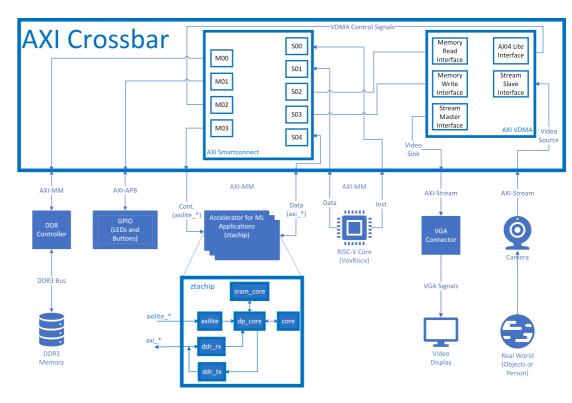

3. In the last objective of our project, we aim to integrate the VexRiscv processor and ztachip (hardware accelerator) on an FPGA kit. One of the significant advantages of using an FPGA is its reconfigurability, even after the synthesis of a circuit. Moreover, an FPGA requires less board space and is more energy-efficient compared to an equivalent discrete circuit or ASIC (Application Specific Integrated Circuits). The kit used for this project is Genesys 2 Kintex-7 (xc7k325t-2ffg900C). Then the results generated by the integrated system will be compared with other accelerators out there in terms of speed, performance and memory usage.

### 1.5 Project Scope

#### 1.5.1 RISC-V

RISC-V has bright future. RISC-V is now using in companies and companies are taking benefit from it to build custom processors for newer technologies' power and performance, for example ML (Machine Learning), AI (Artificial Intelligence), and IoTs (Internet of Things).

RISC-V is now using for edge computing to cloud servers and HPC (High-Performance Computing). However, companies are slowly going towards RISC-V for general-purpose processors which can be used in dashtops, laptops, and data centers. According to the RISC-V International Foundation, they expect the adoption of RISC-V over the entire CPU spectrum by 2025. Several companies and academic institutions are currently developing RISC-V-based processors that are expected to be released in the coming years, including ATSC, Cambridge, Esperanto Technologies, ETH Zurich, NVIDIA, and more. While current RISC-V technologies can't currently compete with x86 offerings from AMD and Intel, there's enough momentum for the open-source instruction set architecture to produce competitive hardware soon.

#### NASA and RISC-V:

Nowadays NASA is planning to use RISC-V power space computer for future space missions. SiFive, a well-known manufacturer of electronic devices based on RISC-V architecture, has signed an agreement with NASA to supply custom RISC-V based processors for the space agency's High-Performance Spaceflight Computer (HPSC). This product is made with the collaboration of SiFive with Microchip and contains 12 cores based on RISC-V ISA and they are expected to offer 100 times more performance than NASA's previously used processor BAE RAD750. [2]

Figure 1.9: NASA selects RISC-V for Space Exploration

Source: EENews

This is a huge step up for the space industry and will allow us to explore the universe and discover many things in a more efficient way and much faster than before. The reason for the growing interest in RISC-V processors is due to their power-efficient design, which follows the same principles as ARM's proprietary cores. However, unlike ARM processors that require royalty payments each time they are incorporated into a chip, RISC-V offers a royalty-free alternative. On the other hand, we all know that RISC-V is a free, open-source ISA and is also flexible in nature. No wonder it is being used from embedded platforms to now in space exploration!

#### **RISC-V** with SiFive:

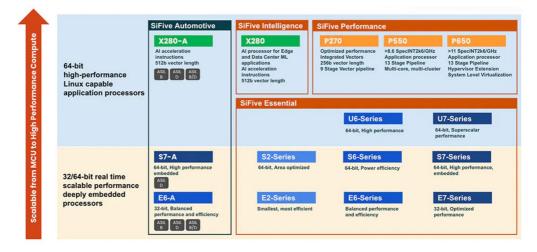

SiFive was established by the creators of RISC-V, who have been working on the RISC-V instruction Set Architecture (ISA) since 2010. Their goal is to empower big and small companies to innovate with the next generation of high-performance processors based on RISC-V. They enable the development of application-specific silicon faster than ever. SiFive has the capability to fully leverage the potential of the open-source RISC-V architecture on a large scale. [3]

Figure 1.10: Description of four Distinct Processor Families of SiFive Core IP Portfolio based on the RISC-V ISA

Source: SiFive

SiFive is working on core IPs and have divided them into four families based on their specifications and necessities.

#### **RISC-V** based Laptops:

It is encouraging to see the increasing adoption and software compatibility of RISC-V processors. The fact that this open-source architecture is now being utilized in tangible products is a positive development. One such product is the Alibaba Roma RISC-V laptop [4], which was announced in the summer and has now become available. This laptop features a quadcore processor and a range of capabilities that are commonly found in Intel and AMD computers. The news was reported by CNX Software.

| Essential details    |                              |                              |                  |

|----------------------|------------------------------|------------------------------|------------------|

| Warranty(Year):      | 5-Year                       | Display Ratio:               | 16:9             |

| Display resolution:  | 1920x1080                    | Port:                        | 2*USB3.0         |

| Series:              | For Business                 | Hard Drive Type:             | SSD              |

| Graphics Card        | Imagination                  | Operating System:            | Linux            |

| Brand:               |                              | Feature:                     | Backlit keyboard |

| Video Memory         | Main memory allocated memory | Thickness:                   | 18 - 20mm        |

| Capacity:            |                              | Processor Main<br>Frequency: | 2.50GHz          |

| Processor Core:      | Quad Core                    | Video Card:                  | N/A              |

| After-sales Service: | Free spare parts             | Products Status:             | New              |

| Type:                | Regular                      | Screen Size:                 | 14.1"            |

| Processor Type:      | N/A                          | Memory Capacity:             | 16GB             |

| Graphics Card Type:  | Integrated Card              | Brand Name:                  | DC-ROMA          |

| Place of Origin:     | China                        |                              |                  |

Figure 1.11: Specification of Alibaba Roma RISC-V Laptop Source: Alibaba.com

Below is some description of RISC-V based laptop available for sale on Alibaba

#### **RISC-V** and Google:

Overview

As we all know that Google requires much computation power for their datacenters. According to SiFive they can fulfill their demand by providing a processor from their intelligence family. The processor of interest here is Intelligence X280 which is a multicore processor based on RISC-V ISA along with vector extensions. This processor is optimized for AI/ML applications and the datacenters of Google also used Machine Learning so this may be a good decision to use this processor. It can be combined with MXU (matrix multiplication units) which are used in the Google's TPUs (Tensor Processing Units). SiFive claims that it will deliver greater flexibility for programming and running machine learning workloads. [5]

Design and Implementation of RISC-V Processor with ML Accelerator 17

Figure 1.12: Google selected SiFive Source: The Register

It has been heard that Google has placed its custom acceleration units in the same chip of SiFive (multicore X280) and it is directly connected to the Google designed MXU blocks. These RISC-V core complex chips are being used in the datacenters, according to SiFive, to speed up the machine learning work.

Additionally, it has been discovered that an all-encompassing software stack was necessary for handling the accelerator, and consumers came to the realization that they could address this concern by employing an X280 core complex in close proximity to their sizeable accelerator. The RISC-V CPU cores are responsible for supervising and executing maintenance and operation code, accomplishing mathematical operations that the large accelerator is incapable of performing, and furnishing diverse other functions. In essence, the X280 has the potential to function as a managerial hub for the accelerator.

#### **RISC-V** and China:

ARM recently stated that RISC-V poses no threat to them in datacenters, but China's interest in RISC-V could prove otherwise. Due to trade bans and restrictions imposed by the US on China, the country has been banned from importing chips from other countries, including x86 processors and AI kit from Intel, AMD, and Nvidia. [6]

Figure 1.13: China showing interest in RISC-V Source: The Register

Chinese companies are increasingly adopting RISC-V as a means to quickly develop their own architecture, bypassing the need for proprietary solutions. This trend is reflected in the fact that a significant portion of RISC-V members are Chinese-based, and that the government-backed Academy of Sciences is actively engaged in developing high-performance, open-source RISC-V processors.

#### 1.5.2 Machine Learning

Machine learning is a powerful tool nowadays and everyone use it such as Amazon, Netflix, Facebook, and so on. Machine learning is so versatile we can take unpredictable benefit from it.

In machine learning we don't need to remember anything, machine learning itself can memorize anything through experiences and trails. Machine learning is an application of Artificial Intelligence, create computer program and assist computer to memorize without the help of human interaction.

## Figure 1.14: Machine Learning, Its Importance, Types, and Applications Source: FORE School of Management

Machine learning plays a crucial role in the field of businesses as it allows entrepreneurs to understand customers' requirements and business functioning behavior. Nowadays many famous companies such as Amazon, Google, Facebook, and many more are professionally exploiting these technologies, and machine learning becoming a core operational part of functionality. The future of machine learning is quite bright and exciting.

Every common field is powered by machine learning applications, some of them are search engine, healthcare, digital marketing, and education. Machine learning is being so noticeable and leading in our lives today, it's challenging and difficult to imagine a future without it.

Design and Implementation of RISC-V Processor with ML Accelerator 21

# Chapter 2

### Literature Review

Design and Implementation of RISC-V Processor with ML Accelerator 22

#### 2.1 Introduction

RISC-V, an open and modular Instruction Set Architecture (ISA), has the potential to revolutionize the Internet of Things (IoT), Artificial Intelligence (AI), and Machine Learning (ML) industries due to its clean design and open nature. Although RISC-V is not the first open processor implementation, it is associated with two keywords - freedom and innovation - as it offers users the freedom to use the cores however they wish. The emergence of RISC-V coincides with other industry events, such as the slowing of Moore's Law and the growth of machine learning, leading to the question of whether the timing is right for RISC-V's success.

Simon Davidmann, CEO and founder of Imperas Software, believes that the RISC-V architecture has gained popularity due to the need for flexibility in the hardware design process. Today's electronic products are defined by their functionality, much of which is dependent on software running on processors. As machine learning becomes increasingly important across all industries, the demand for computing power has skyrocketed, leading to a need for numerous processors configured in a customized manner. Standard off-the-shelf technologies are not sufficient to meet this demand for customization. Therefore, there is a growing demand for the freedom to design chips and processors, as well as the fabrics of processors that go into these chips.

RISC-V is gaining popularity among universities, with many creating open cores and incorporating the RISC-V ISA into their courses. For instance, the University of California, Berkeley has developed Rocket cores using RISC-V and is teaching the architecture to students in their EECS department. Likewise, ETH Zurich has created power-efficient cores like ibex, zero-riscy, micro-riscy, and others using their PULP platform. Several industry collaboration groups such as CHIPS Alliance, OpenHW Group, and SiFive are working together with both industry and academia to build open-source cores and make them widely available to the community.

#### 2.2 Purpose of the Review

The purpose of this literature review is to let the readers know about the advancements to RISC-V in industrial area as well as in educational and innovational region. Also, we are going to compare a few examples of RISC-V ISA being used nowadays in many applications with our processor and accelerator and have a detailed discussion on their uses.

#### 2.3 RISC-V based Pakistan's first processor

NUST [7] has Developed Pakistan's First Self-Developed Embedded Microprocessor NTiny-E. Electronic devices and consumer appliances rely heavily on semiconductor chips. In 2021, global semiconductor sales exceeded \$556 billion. However, Pakistan has yet to tap into this lucrative market.

Figure 2.1: NUST developed Pakistan's First Processor based on RISC-V Source: propakistani

In pursuit of its objective to promote applied research and innovation, the National University of Sciences and Technology (NUST) initiated an effort to make Pakistan self-sufficient in semiconductor technology. As a result of this endeavor, researchers at NUST have accomplished comprehensive functional testing of the NTiny-E microprocessor, which is the first-ever domestically developed microprocessor in the country, based on the RISC-V ISA. This microprocessor has been fabricated by Taiwan Semiconductor Manufacturing Company, Limited using a 65nm process node, and is aimed towards the market for embedded systems, consumer electronic products, and IoT devices.

|             | Feature | Description                                           |  |

|-------------|---------|-------------------------------------------------------|--|

| CORE BASE   | RV32I   | 32-Bit Integer Base                                   |  |

| Extensions  | М       | Integer Multiplication and Division                   |  |

| Extensions  | F       | IEEE Single-Precision Floating Point                  |  |

| Momony      | IMEM    | Instruction Memory 32KB                               |  |

| Memory      | DMEM    | Data Memory 8KB                                       |  |

| Peripherals | UART    | Universal Async. Receiver Transmitter                 |  |

|             | I2C     | Inter Integrated Circuit                              |  |

|             | SPI     | Serial Peripheral Interface                           |  |

|             | GPIO    | General Purpose I/O - 16                              |  |

|             | Timer   | 32-Bit 1x Timer                                       |  |

|             | PWM     | Pulse Width Modulation-2x                             |  |

|             | JTAG    | IEEE complaint JTAG support for in-system programming |  |

|             | Debug   | OpenOCD Debug support                                 |  |

Following is the table containing some of its specifications:

Table 2.1: Specifications of NTiny-E

Source: propakistani

#### 2.4 UC Berkeley made RISC-V Chips

As we all know RISC-V was a project of UC Berkeley, California. They have also designed many open source cores but in we will be talking about a few of them which are prominent.

Rocket Chip is an open-source System-on-Chip design generator that can create a synthesizable RTL using Chisel HDL, a different approach to traditional hardware description languages. The output is a library of generators for cores, caches, and interconnects that can be integrated into a complete SoC. The generated processor cores are based on the RISC-V ISA, including both in-order (Rocket) and out-of-order (BOOM) core generators. Additionally, Rocket Chip can accommodate custom accelerators, such as instruction set extensions, coprocessors, or new independent cores. By using Rocket Chip, functional silicon prototypes that can boot Linux have been successfully produced. [8]

Another core generator of note is BOOM (Berkeley Out-of-Order Machine), which is a superscalar RV64G core generator designed to serve as a base implementation for research, industry, and education for extensive exploration of out-of-order microarchitecture. BOOM features an advanced load/store unit that enables loads to execute out of order with respect to other loads and stores, as well as store data forwarding to dependent loads. It is developed in Chisel HDL and consists of approximately 10,000 lines of code. [9]

A 45nm SOI process has been used to develop a 64-bit dual-core RISC-V processor with vector accelerators, making it the first dual-core processor produced using the open-source RISC-V ISA created at the University of California, Berkeley. When compared to ARM's similar single-issue inorder scalar core, the RISC-V scalar core surpasses in DMIPS/MHz by 10%, while being 49% more area-efficient, all made in a standard 40nm process. Furthermore, the vector accelerator in this RISC-V processor consumes  $1.8 \times$  less energy than IBM Blue Gene/Q and  $2.6 \times$  less than the IBM Cell processor, which were both made using the same process. This dual-core RISC-V processor has a maximum clock frequency of 1.3GHz at 1.2V and can achieve a peak energy efficiency of 16.7 double-precision GFLOPS/W at 0.65V, all within a compact 3mm area. [10]

### 2.5 Power Management Integrated RISC-V Processor SoC Operating at Submicrosecond Timescales

An efficient RISC-V system-on-chip (SoC) has been designed that combines voltage regulation, adaptive clocking, and power management in a single chip using a 28 nm fully depleted silicon-on-insulator process. The SoC features a simultaneous-switching switched-capacitor DC-DC converter that supplies an application core using a clock generated by an adaptive clock generator. The SoC is highly efficient, with conversion efficiency of 82%-89% and energy efficiency of 41.8 double-precision GFLOPS/W, while consuming up to 231 mW of power. The integrated power-management unit measures the state of the system and adjusts the voltage and frequency of the core, allowing the implementation of power-management algorithms that can respond at submicrosecond timescales. The system has a wide continuous voltage range of 0.45 V-1 V, and an adaptive voltage-scaling algorithm that can reduce energy consumption by 39.8% during synthetic benchmark testing. The system is effective at managing power consumption and has only 2.0% area overhead. [11]

### 2.6 RISC-V Processor Designed for Space Systems

A low-cost fault-tolerant implementation of the RISC-V architecture is proposed. The implementation employs physical and information redundancy to reduce error propagation, which is critical for space systems where reliability is paramount. Physical redundancy involves replicating the hardware components, while information redundancy involves duplicating the data and comparing it to detect errors. The proposed implementation achieves fault tolerance through several techniques. One of these is the use of a dual modular redundancy (DMR) technique, which involves replicating the processor's logic and executing the same instruction on both replicas simultaneously. The output of each replica is then compared to detect errors, and the correct output is selected.

In addition to DMR, the proposed implementation employs other faulttolerant techniques, such as error-correcting codes (ECC) for memory and data paths, and parity checks for control logic. These techniques help to detect and correct errors in the system, making it more reliable.

The proposed implementation also achieves competitive silicon and power overheads when compared with other RISC-V implementations. This is important in space systems, where size, weight, and power consumption are critical factors. [12]

#### 2.7 RISC-V and PULP

In 2013, the Integrated Systems Laboratory (IIS) at ETH Zürich and the Energy-efficient Embedded Systems (EEES) group at the University of Bologna joined hands to create the Parallel Ultra-Low-Power Processing Platform (PULP). Its objective is to research and develop innovative and effective architectures for processing with ultra-low power consumption.[15] In the following discussion, we will delve into several of their cores and their specifications.

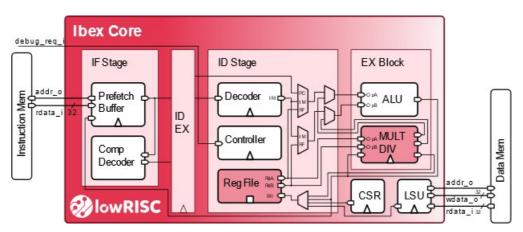

#### 2.7.1 Ibex Core

To begin with, the Ibex RISC-V Core is a 32-bit CPU core designed in SystemVerilog and available as open-source. [16] This core is highly customizable and ideal for embedded control applications. It has undergone rigorous verification and has been used in multiple tape-outs. Ibex supports various extensions, including Integer (I) or Embedded (E), Integer Multiplication and Division (M), Compressed (C), and Bit Manipulation (B). The core's block diagram indicates a small parameterization with a 2-stage Pipeline.

Figure 2.2: Ibex Core Block Diagram

#### Source: GitHub

This block diagram shows various stages of this CPU. We have IF stage whose job is to fetch the instruction from instruction memory and also to check if the instruction is compressed or uncompressed one.

Then we have ID stage whose job is to decode the given instructions and generate the control signals to perform the required task. It also contains GPR which stands for general purpose registers. There quantity may vary on the configuration being used. If we are using micro-riscy then the no. of registers here will be 16 and other than this configuration total registers will be 32. No matter what the configuration is the register size will remain the same which is 32 bits.

At last, we have EX block whose job is to execute the desired operation using ALU (arithmetic and logic unit) and MultDiv block for multiplication and division. Other than these main blocks it also contains CSRs which stands for Control and Status registers. These registers are used for different purposes including flags and interrupts etc. We also have LSU (load store unit) whose job is to store or load any data to or from the data memory respectively.

Here is a table that displays the performance and area of selected configurations that lowRISC is concentrating on for evaluating performance and verifying designs.

| Config                               | "micro" | "small"                  | "maxperf"                                                          | "maxperf-pmp-bmfull"                                                                   |

|--------------------------------------|---------|--------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Features                             | RV32EC  | RV32IMC,<br>3 cycle mult | RV32IMC,<br>1 cycle mult,<br>Branch target ALU,<br>Writeback stage | RV32IMCB,<br>1 cycle mult,<br>Branch target ALU,<br>Writeback stage,<br>16 PMP regions |

| Performance<br>(CoreMark/MHz)        | 0.904   | 2.47                     | 3.13                                                               | 3.13                                                                                   |

| Area - Yosys<br>(kGE)                | 16.85   | 26.60                    | 32.48                                                              | 66.02                                                                                  |

| Area - Commercial<br>(estimated kGE) | ~15     | $\sim 24$                | ~30                                                                | ~61                                                                                    |

| Verification status                  | Red     | Green                    | Green                                                              | Green                                                                                  |

Table 2.2: Comparison of Different PULP Cores

Source: GitHub

#### 2.7.2 Zeroriscy Core

Now finally this is the core we have been working on as a starting point. As it can be seen in the previous table that it is derived from Ibex core and is also area and power efficient. Zeroriscy is a specific implementation of the RISC-V instruction set architecture, designed to be a small and efficient 32-bit processor core. It is an in-order processor with a 2-stage pipeline, meaning that it processes instructions in a linear sequence and has two stages of processing. [21]

The design of zeroriscy is configurable, allowing it to support four different ISA (instruction set architecture) configurations, which are determined by two parameters. This configurability allows the processor core to be tailored to specific use cases or requirements, such as optimizing for power efficiency or maximizing performance.

Design and Implementation of RISC-V Processor with ML Accelerator 31

The RISC-V instruction set architecture, which zeroriscy is based on, is an open-source architecture that is gaining popularity in both academic and industrial settings. Its modular design and flexibility make it a suitable choice for a wide range of applications, from small microcontrollers to high-performance computing systems. Ibex contains an extra extension of Bit Manipulation (B). Interesting thing is that zeroriscy can further be configured and get smaller named as micro-riscy. The difference between two of them is that zeroriscy support I base extension containing 32 temporary core registers while micro-riscy supports E extension, short-form for Embedded, and only contains 16 base registers instead of 32. [17]

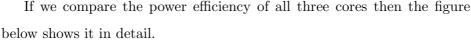

below shows it in detail. 0.6 0.55 prefetcher-buff 0.506 0.5 register-file 0.464 30.9% ctr-status RF ₹0.45 load-store unit 0.4 decoder+ctrl

Source: Semantic Scholar

As we can see in this graph that they consume power in similar order

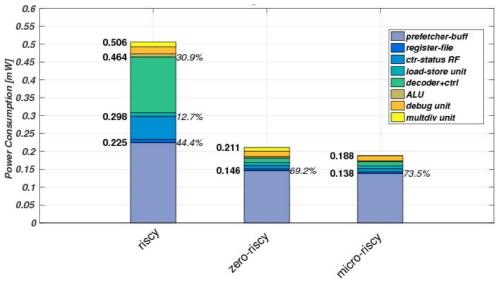

as they are constructed. zero-riscy consums merely 0.211 mW of maximum power even if its multiplier is running. Now if we compare the area of all the other PULP cores then the figure below shows in detail.

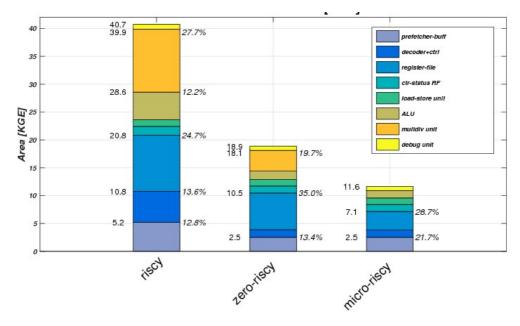

Figure 2.4: The Total Area Occupied by all the Core Units in KGE (thousands of square millimeters)

As we can see in the above graph that the total area covered by zeroriscy is only 18.9 KGE (Kilo Gate Equivalent). Now if we take a look at the figure below of its block diagram.

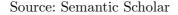

This block diagram shows different parts/modules of this core. For example pre-fetch buffer has the job of fetching instructions one by one from the instruction memory and either send it to ID stage or store it in a FIFO if exceptional cases occur. Debug unit is used to debug any error or issues related to the hardware of the processor. Decoder decodes the given 32 bit instruction and some part goes to the GPR (General Purpose

Figure 2.5: Block Diagram of zeroriscy Core Source: Semantic Scholar

Register) and some goes to Controller to generate control signals. ALU has the capability to perform addition of any type of two operands whether registers, immediates or PCs and it also performs subtraction, shifting and other logical operations. MultDiv block performs, as depicts from the name, multiplication and division. It uses 3 cycle multiplier and 36 cycle divider. CSR (Control and Status Registers are special purpose registers. LSU stands for Load store unit and its job is to either store or load the date to or from memory respectively. This was all for now about zeroriscy core.

#### Supported Instruction Set:

Zeroriscy supports the following RISC-V instruction sets:

- RV32I Base Integer Instruction Set: It consists of fundamental instructions for performing integer arithmetic, logical operations, load and store operations, as well as control transfer instructions.

- RV32E Base Integer Instruction Set: This instruction set is a subset of

the RV32I instruction set, designed for embedded systems with limited resources. It includes a smaller set of instructions and a smaller register file.

- RV32C Standard Extension for Compressed Instructions: This instruction set provides support for compressed instructions, which can reduce code size and improve memory bandwidth.

- RV32M Integer Multiplication and Division Instruction Set Extension: This instruction set provides support for integer multiplication and division operations.

- The RV32M and RV32E extensions can be enabled or disabled using two parameters, allowing for flexibility in configuring the processor core to meet specific requirements. Enabling the RV32M extension adds support for integer multiplication and division instructions, while enabling the RV32E extension switches to the RV32E instruction set, which is a more compact subset of the RV32I instruction set.

Overall, zeroriscy's support for these instruction sets and its configurability make it a versatile and efficient choice for a wide range of applications. [17]

#### Instruction Fetch:

If the memory or cache can also provide one instruction per cycle, the instruction fetcher can deliver one instruction to the next stage of the processor per cycle. It is important to note that the instruction address must be half-word-aligned to enable the use of compressed instructions. [18]

To further optimize performance, a prefetcher is used to fetch instructions ahead of time so that they are ready when needed.Jumping to an instruction address with the least significant bit set is not feasible.

Overall, these signals and requirements help ensure that instructions are fetched efficiently and correctly, allowing the processor to operate at peak performance.

| Signal              | Direction | Description                          |  |

|---------------------|-----------|--------------------------------------|--|

|                     |           | Request ready, must stay high        |  |

| instr_req_o         | output    | until instr_gnt_i is high for one    |  |

|                     |           | cycle                                |  |

| instr_addr_o[31:0]  | output    | Address                              |  |

| instr_rdata_i[31:0] | input     | Data read from memory                |  |

| instr_rvalid_i      | input     | instr_rdata_is holds valid data      |  |

|                     |           | when instr_rvalid_i is high.         |  |

|                     |           | This signal will be high for         |  |

|                     |           | exactly one cycle per request.       |  |

|                     | input     | The other side accepted the request. |  |

| instr_gnt_i         |           | instr_addr_o may change in the next  |  |

|                     |           | cycle                                |  |

Table 2.3: Instruction Fetch Signals

Source: zero-riscy User Manual

#### Load-Store-Unit (LSU):

The Load-Store Unit (LSU) is a component of a processor core that facilitates access to data memory, where the processor stores the data that it needs to operate on. It is specifically designed to handle data of varying sizes, such as 32-bit words, 16-bit half-words, and 8-bit bytes. A "load" operation in the LSU retrieves data from memory and stores it in a register within the processor. This operation is used when the processor needs to read data from memory, for example, to read the value of a variable.

A "store" operation in the LSU writes data to memory. This operation is used when the processor needs to update the value of a variable or store new data in memory.

The LSU supports different data sizes to allow for more efficient memory access. For example, when the processor only needs to read or write 16 bits of data, it can use a half-word load or store operation, which is faster than a full word operation. Similarly, a byte load or store operation can be used when the processor only needs to access 8 bits of data. [18]

| Signal             | Direction | Description                          |  |

|--------------------|-----------|--------------------------------------|--|

|                    | output    | Request ready, must stay high        |  |

| data_req_o         |           | until data_gnt_i is high for one     |  |

|                    |           | cycle                                |  |

| data_addr_o[31:0]  | output    | Address                              |  |

|                    | output    | Write Enable, high for writes,       |  |

|                    |           | low for reads. Sent together with    |  |

| data_we_o          |           | data_req_o data_be_o[3:0] output     |  |

| data_we_o          |           | Byte Enable. Is set for the bytes    |  |

|                    |           | to write/read, sent together with    |  |

|                    |           | data_req_o                           |  |

| data_wdata_o[31:0] | output    | Data to be written to memory,        |  |

| uata_wuata_0[51.0] |           | sent together with data_req_o        |  |

| data_rdata_i[31:0] | input     | Data read from memory                |  |

|                    | input     | data_rdata_is holds valid data when  |  |

| data_rvalid_i      |           | data_rvalid_i is high. This signal   |  |

|                    |           | will be high for exactly one cycle   |  |

|                    |           | per request.                         |  |

|                    | input     | The other side accepted the request. |  |

| data_gnt_i         |           | data_addr_o may change in the next   |  |

|                    |           | cycle                                |  |

Table 2.4: LSU Signals

Source: zero-riscy User Manual

#### **Register File:**

The zeroriscy processor core is based on the RISC-V architecture and provides either 31 or 15 32-bit wide registers, depending on whether the RV32E  $\,$

extension is activated. Register x0 is permanently assigned to the value 0 and cannot be modified.

Zeroriscy has two types of register files: a latch-based register file and a flip-flop based register file. The former is suggested for ASICs, while the latter is recommended for FPGA synthesis. However, both types of register files are suitable for either type of synthesis.

When implemented in an ASIC, the flip-flop based register file is considerably larger compared to the latch-based register file. This is because ASICs are optimized for power efficiency and the latch-based register file consumes less power than the flip-flop based register file. On the other hand, in FPGA synthesis, power consumption is not a major concern, and the flip-flop based register file is suggested as it exhibits superior performance and timing characteristics.

In general, the selection of register file type relies on the target platform and implementation details. Even though both register file types work with either synthesis target, the latch-based register file is more powerefficient for ASICs. In contrast, the flip-flop based register file has better timing characteristics and performance, which makes it a suitable option for FPGA synthesis. [18]

### 2.8 RISC-V Accelerator for Post-Quantum Cryptography

Post-Quantum Cryptography (PQC) introduces new mathematical elements and operations that are challenging to implement on standard processors, particularly for low-cost and resource-constrained devices. Hardware acceleration is typically required to support PQC on these devices. Additionally, the ongoing standardization process of PQC requires maintaining flexibility in the design. Although co-design techniques that incorporate hardware and software have been utilized to create intricate and personalized post-quantum cryptography (PQC) solutions, the development of tightly integrated accelerators and Instruction Set Architecture (ISA) extensions for PQC has not been extensively investigated.

The proposal of the authors is the RISQ-V, which is an improved version of the RISC-V architecture. It integrates tightly coupled accelerators that enhance the performance of lattice-based PQC. The RISQ-V design optimizes processor resources and reduces the memory access needed, resulting in increased performance with minimal silicon area overhead. [13]

#### 2.9 RISC-V Accelerator designed for Ascon

ASCON-p is a cryptographic module that has a low weight and can perform various cryptographic tasks such as hashing, authenticated encryption, and pseudorandom number generation. It is based on a permutation, which is a mathematical operation that shuffles the input data in a way that is difficult to reverse.ASCON-p is a cryptographic building block that has multiple applications, including authenticated encryption, hashing, and pseudorandom number generation. One of its implementations is ASCON, which is a lightweight authenticated encryption algorithm and won the lightweight category of the CAESAR competition. Another implementation is ISAP, an AEAD (Authenticated Encryption with Associated Data) scheme that uses ASCON-p and is currently a competitor in the NIST lightweight cryptography standardization project.

The researchers have implemented ASCON-p as an instruction extension for the RISC-V processor, which is a popular open-source processor architecture used in many embedded devices. This instruction extension is tightly coupled to the processor's register file, which means it does not require any dedicated registers. With this implementation, cryptographic computations can be performed with high performance, and the performance is even better if protection against fault attacks and power analysis is desired.

The researchers have also shown that their implementation is very efficient and requires only a small amount of area, making it suitable for low-end embedded devices like 32-bit ARM Cortex-M or RISC-V microprocessors. The authors conducted a performance evaluation of their implementation, utilizing the AEAD modes and hashing algorithms of the ISAP and ASCON families. Their results demonstrated that cryptographic computations can be executed at a performance rate of approximately 2 cycles per byte. However, if protection against fault attacks and power analysis is required, the performance rate increases to about 4 cycles per byte.

Finally, the researchers have analyzed the implementation security of ISAP when implemented using their instruction extension. They have shown that their implementation provides strong protection against a large class of implementation attacks such as DPA, DFA, SFA, and SIFA. This means that the cryptographic computations performed using their implementation are secure against these attacks, which are commonly used to break cryptographic systems. [14]

## Chapter 3

### **RISC-V** Processor

Design and Implementation of RISC-V Processor with ML Accelerator 42

#### 3.1 Introduction

RISC-V is a contemporary Instruction Set Architecture (ISA) with a clean and modular design that has the potential to become a significant player in the era of Artificial Intelligence (AI), Machine Learning (ML), and the Internet of Things (IoT) due to its open nature. Although it is not the first time a processor implementation or ISA has been declared open for public use, RISC-V is associated with two key concepts - freedom and innovation. Some users seek freedom to use cores, while others desire the freedom to modify them as needed. The increasing popularity of RISC-V coincides with the slowing of Moore's Law and the remarkable growth of machine learning. Is this just a fortuitous coincidence?

According to Simon Davidmann, the CEO of Imperas Software, the RISC-V architecture has gained popularity due to the demand for greater freedom in the hardware design process community. In today's electronic products, which heavily rely on software running on processors, machine learning is essential. This has led to a need for numerous processors, and the ability to configure them in a customized manner. People realized that offthe-shelf technologies were not sufficient, and they required more freedom to design chips and their processors. Therefore, there has been a shift in the electronic product marketplace that seeks greater freedom in architecting chips and the processors that operate within them.

Various academic institutions have contributed to the development and education of the RISC-V ISA. Some have created open-source cores and are incorporating RISC-V into their courses. The University of California, Berkeley, for instance, has designed Rocket cores based on RISC-V and is teaching the ISA to its EECS students. Similarly, ETH Zurich has developed power-efficient cores such as ibex, zero-riscy, micro-riscy, and others through its PULP platform. Collaboration groups involving both academia and industry, such as CHIPS Alliance, OpenHW Group, and SiFive, are also working on building open-source cores and making them available to the wider community.

#### 3.2 VexRiscv

VexRiscv is an open-source RISC-V processor implemented in the Spinal-HDL language, which can be synthesized for various FPGA platforms. The version of VexRiscv processor used in this project is MyVexRiscv, with some modifications and additions to VexRiscv's default configuration. [1]

MyVexRiscv has a simple, yet powerful architecture. It is a 32-bit RISC-V processor that supports the RV32IMC instruction set, which includes the basic integer arithmetic and logic operations, load and store instructions, control transfer instructions, multiplication and division capability, compressed instructions, and system calls. The processor also includes additional instructions provided by the VexRiscv plugins, such as barrel shifter instructions, early branching etc.

The processor is highly configurable, with a set of CPU plugins that can be added or removed depending on the user's needs. These plugins include a cached instruction bus, a cached data bus, a CSR (Control and Status Register) plugin, a simple decoder plugin, a memory translator plugin, a register file plugin, an integer ALU plugin, a source plugin, a full barrel shifter plugin, a hazard plugin, a multiplication plugin, a division plugin, a branch plugin, and a YAML plugin.

The processor also includes peripherals such as an APB (Advanced Peripheral Bus) controller, an AXI (Advanced eXtensible Interface) controller, a JTAG (Joint Test Action Group) controller, a timer, a prescaler, and a DDR (Double Data Rate) SPI (Serial Peripheral Interface) master controller.

The processor is designed to be synthesized for FPGAs, with a simple interface that allows it to be easily integrated into larger systems. The processor's clock domain can be configured to run at a maximum frequency of 166 MHz. It works on little endian memory storage with 8K of instruction and data cache.

Overall, MyVexRiscv is a flexible and powerful RISC-V processor that can be customized to meet a wide range of embedded system design requirements. It provides a robust platform for developing FPGA-based systems with RISC-V processors, and is well-suited for applications such as robotics, machine learning, and embedded vision.

#### 3.2.1 Performance Score Comparison

MyVexRiscv processor has achieved benchmark scores of 1.38 DMIPS/Mhz and 2.57 Coremark/Mhz. These scores are with configuration of single cycle barrel shifter, debug module, catch exceptions, dynamic branch prediction in the fetch stage, branch and shift operations done in the Execute stage These scores indicate the performance of the processor in terms of instructions executed per second (DMIPS) and its ability to handle real-world workloads (Coremark).

While these scores may not be the highest in the industry, they still demonstrate that MyVexRiscv is a capable processor that can handle a wide range of tasks. Additionally, it's important to note that benchmarks are just one measure of a processor's performance, and real-world performance can vary based on a variety of factors such as the specific workload, memory configurations, and software optimizations.

Following is the table which includes benchmark scores [22] of other

| Processors:    | Coremark/MHz | DMIPS/MHz |

|----------------|--------------|-----------|

| MyVexRiscv     | 2.57         | 1.38      |

| (RV32IMC ISA)  | 2.01         |           |

| Cortex-M0+     | 1.8          | 0.95      |

| (ARMv6-M ISA)  | 1.0          |           |

| Cortex-M4      | 2.76         | 1.25      |

| (ARMv7-M ISA)  | 2.10         |           |

| SiFive E21     | 3.1          | 1.38      |

| (RV32IMAC ISA) | 5.1          |           |

| SiFive E20     | 2.4          | 1.1       |

| (RV32IMC ISA)  | 2.1          |           |

RISC-V and ARM cores for comparison with VexRiscv:

Table 3.1: Benchmark Score Comparison of Different Processors

Source: RISC-V Foundation

# Chapter 4

# RISC-V Accelerator for ML Applications

Design and Implementation of RISC-V Processor with ML Accelerator 47

#### 4.1 Introduction

Ztachip is a hardware accelerator designed for low-end FPGA devices or custom ASICs, which aims to provide significant performance improvements for vision and AI edge applications. It has the ability to speed up various tasks, such as executing TensorFlow AI models and performing common vision tasks, such as motion detection, color conversion, optical flow, and edge detection.

Ztachip's acceleration is achieved through the implementation of an innovative tensor processor hardware, which allows for massive processing and data parallelism. This tensor processor hardware is capable of performing a range of tasks, and it is one of the key differences between ztachip and other accelerators that typically only accelerate a narrow range of applications, such as convolution neural networks.